- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDRx的关键技术介绍(下)

录入:edatop.com 点击:

作者:一博科技

今天要介绍的是DDR3和DDR4最关键的一些技术,write leveling以及DBI功能。

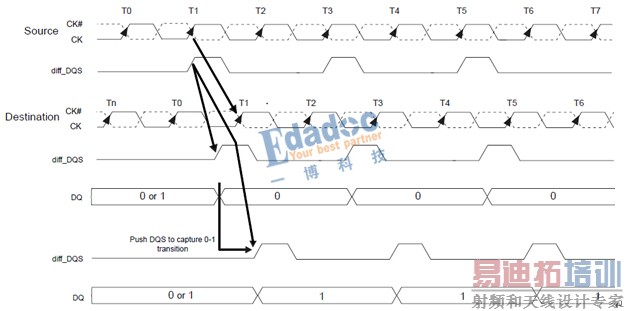

Write leveling功能与Fly_by拓扑

Write leveling功能和Fly_by拓扑密不可分。Fly_by拓扑主要应用于时钟、地址、命令和控制信号,该拓扑可以有效的减少stub的数量和他们的长度,但是却会导致时钟和Strobe信号在每个芯片上的飞行时间偏移,这使得控制器(FPGA或者CPU)很难保持tDQSS、tDSS 和tDSH这些参数满足时序规格。因此write leveling应运而生,这也是为什么在DDR3里面使用fly_by结构后数据组可以不用和时钟信号去绕等长的原因,数据信号组与组之间也不用去绕等长,而在DDR2里面数据组还是需要和时钟有较宽松的等长要求的。DDR3控制器调用Write leveling功能时,需要DDR3 SDRAM颗粒的反馈来调整DQS与CK之间的相位关系,具体方式如下图一所示。

Write leveling 是一个完全自动的过程。控制器(CPU或FPGA)不停的发送不同时延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器。控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变(说明tDQSS参数得到了满足),控制器就锁住此时的延时值,此时便完成了一个Write leveling过程;同时在Leveling 过程中,DQS-DQS#从控制器端输出,所以在DDR3 SDRAM 侧必须进行端接;同理,DQ 线由DDR3 SDRAM颗粒侧输出,在控制器端必须进行端接;

需要注意的是,并不是所有的DDR3控制器都支持write leveling功能,所以也意味着不能使用Fly_by拓扑结构,通常这样的主控芯片会有类似以下的描述:

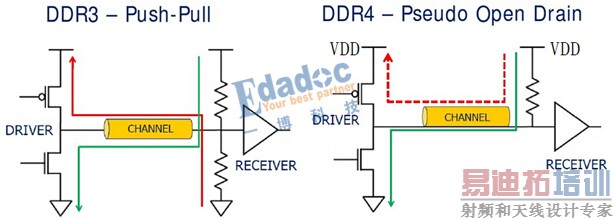

DBI功能与POD电平

DBI的全称是Data Bus Inversion数据总线反转/倒置,它与POD电平密不可分,它们也是DDR4区别于DDR3的主要技术突破。

POD电平的全称是Pseudo Open-Drain 伪漏极开路,其与DDR3对比简单的示例电路如下图二所示。

从中可以看到,当驱动端的上拉电路导通,电路处于高电平时(也即传输的是“1”),此时两端电势差均等,相当于回路上没有电流流过,但数据“1”还是照样被传输,这样的设计减少了功率消耗。

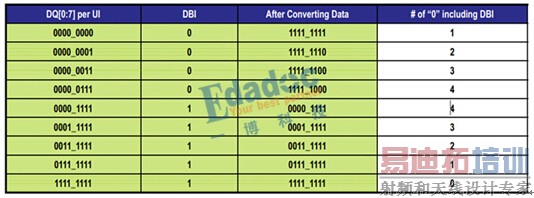

正是由于POD电平的这一特性,DDR4设计了DBI功能。当一个字节里的“0”比特位多于“1”时,可以使能DBI,将整个字节的“0”和“1”反转,这样“1”比“0”多,相比原(反转前)传输信号更省功耗,如下表一所示。

以上就是DDRx的一些主要的关键技术介绍,可以用如下表二所示来总结下DDRx的特性对比。

今天要介绍的是DDR3和DDR4最关键的一些技术,write leveling以及DBI功能。

Write leveling功能与Fly_by拓扑

Write leveling功能和Fly_by拓扑密不可分。Fly_by拓扑主要应用于时钟、地址、命令和控制信号,该拓扑可以有效的减少stub的数量和他们的长度,但是却会导致时钟和Strobe信号在每个芯片上的飞行时间偏移,这使得控制器(FPGA或者CPU)很难保持tDQSS、tDSS 和tDSH这些参数满足时序规格。因此write leveling应运而生,这也是为什么在DDR3里面使用fly_by结构后数据组可以不用和时钟信号去绕等长的原因,数据信号组与组之间也不用去绕等长,而在DDR2里面数据组还是需要和时钟有较宽松的等长要求的。DDR3控制器调用Write leveling功能时,需要DDR3 SDRAM颗粒的反馈来调整DQS与CK之间的相位关系,具体方式如下图一所示。

图一、 Write leveling

Write leveling 是一个完全自动的过程。控制器(CPU或FPGA)不停的发送不同时延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器。控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变(说明tDQSS参数得到了满足),控制器就锁住此时的延时值,此时便完成了一个Write leveling过程;同时在Leveling 过程中,DQS-DQS#从控制器端输出,所以在DDR3 SDRAM 侧必须进行端接;同理,DQ 线由DDR3 SDRAM颗粒侧输出,在控制器端必须进行端接;

需要注意的是,并不是所有的DDR3控制器都支持write leveling功能,所以也意味着不能使用Fly_by拓扑结构,通常这样的主控芯片会有类似以下的描述:

DBI功能与POD电平

DBI的全称是Data Bus Inversion数据总线反转/倒置,它与POD电平密不可分,它们也是DDR4区别于DDR3的主要技术突破。

POD电平的全称是Pseudo Open-Drain 伪漏极开路,其与DDR3对比简单的示例电路如下图二所示。

图二 POD示意电路

从中可以看到,当驱动端的上拉电路导通,电路处于高电平时(也即传输的是“1”),此时两端电势差均等,相当于回路上没有电流流过,但数据“1”还是照样被传输,这样的设计减少了功率消耗。

正是由于POD电平的这一特性,DDR4设计了DBI功能。当一个字节里的“0”比特位多于“1”时,可以使能DBI,将整个字节的“0”和“1”反转,这样“1”比“0”多,相比原(反转前)传输信号更省功耗,如下表一所示。

表一 DBI示例

以上就是DDRx的一些主要的关键技术介绍,可以用如下表二所示来总结下DDRx的特性对比。

表二 DDRx SDRAM特性对比

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>