- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于FPGA的群路信号数字分路实现结构

由于具有高集成度、高速、可编程等优点,现场可编程门阵列(Field Programmable Gate Array,FPGA)已经被广泛应用于中高速群路解调处理领域。数字分路技术是全数字群解调器的重要组成部分,也是群解调器实现过程中消耗硬件资源较大的部分,所以设计合理的分路实现结构将对整个解调器的处理速度和硬件开销产生较大影响。目前,采用FPGA实现数字分路主要存在的问题是FPGA芯片中乘法器资源受限。因此,在已知硬件FPGA芯片乘法器资源约束条件下,设计更为有效的数字分路实现结构是目前重要的研究内容。

1 算法结构

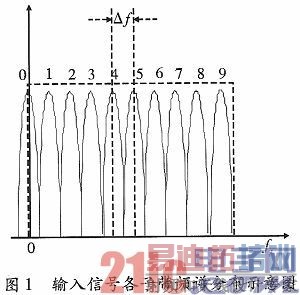

针对输入信号各子带在频域中是按偶型堆积排列和均匀分割的,如图1所示,可采用均匀DFT滤波器组实现其有效数字分路。在图1中,输入信号的基本参数如下:(1)每路载波的符号速率为R=2 Msample·s-1;(2)载波间隔为△f=3.2 MHz;(3)采样速率为Fs=32 MHz。

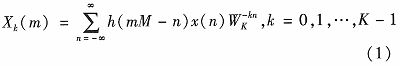

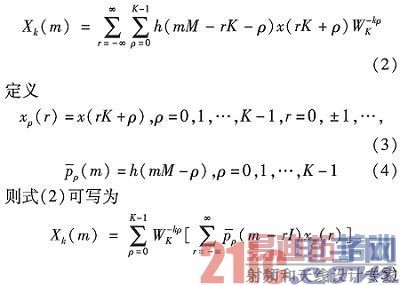

图2给出了单个支路信号处理原理示意图。输入信号首先采用复指数序列e-jωk进行调制(其中,ωk=![]() ,k=0,1,2,…,K-1为第k个子带的中心频率,K为分路路数);然后再将调制后的信号经过低通滤波器进行滤波;最后将滤波后的信号进行降采样(降采样率为M),得到第k个子带信号。该数学模型可表示为

,k=0,1,2,…,K-1为第k个子带的中心频率,K为分路路数);然后再将调制后的信号经过低通滤波器进行滤波;最后将滤波后的信号进行降采样(降采样率为M),得到第k个子带信号。该数学模型可表示为

其中,x(n)表示输入信号;h(n)表示分析滤波器;

;K表示分路路数;M表示降采样率。根据这一数学模型,基于均匀DFT滤波器组数字分路技术,有基于多相结构和加权叠接-相加结构两种实现结构。

由于输入信号速率为32 MHz,各子带频率间隔为3.2 MHz,则分路路数K=32/3.2=10。又由于每路输出信号速率为2×4=8 MHz,则降采样率M=32/8=4,因此逻辑上可以按照K=M(其中,I=2.5)形式的多相结构实现数字分路。

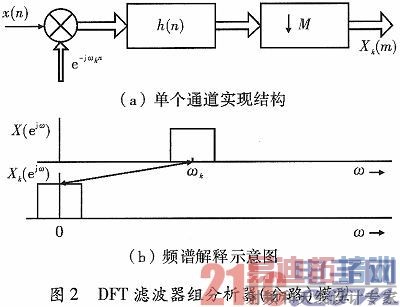

在式(1)中,通过变量置换n=rK+ρ,ρ=0,1,…,K-1,得到

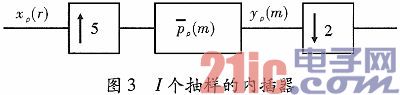

式(5)的括号中定义了一个I个抽样的内插器,令yρ(m)是内插器的输出,则该项对应的数学模型如图3所示。

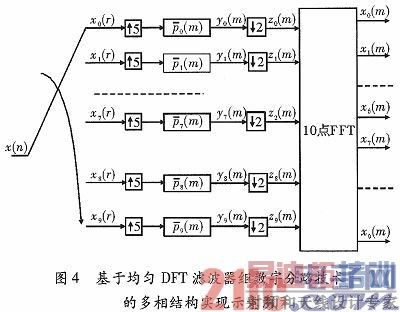

根据式(5)所示,则基于均匀DFT滤波器组数字分路技术实现结构如图4所示,具体实现步骤如下

(1)对输入信号x(n)进行10路并行转换,得到10路子信号xρ(r),ρ=0,1,…,9,此时信号速率由fs=32 MHz变为f=32 MHz/10=3.2 MHz。

(2)对每一路子信号xρ(r)进行5倍速率内插,并分别采用对应的滤波器*

进行滤波,得到10路输出信号yρ(m),每一路对应的滤波器

可以由分析滤波器h(n)按照式(4)得到,此时信号yρ(m)的速率由3.2 MHz变为3.2 MHz×5=16 MHz。

(3)对10路yρ(m)信号分别进行2倍下采样,变为zρ(m)。

(4)对上述得到的10路并行信号进行10点FFT计算,得到分路后的10路信号。

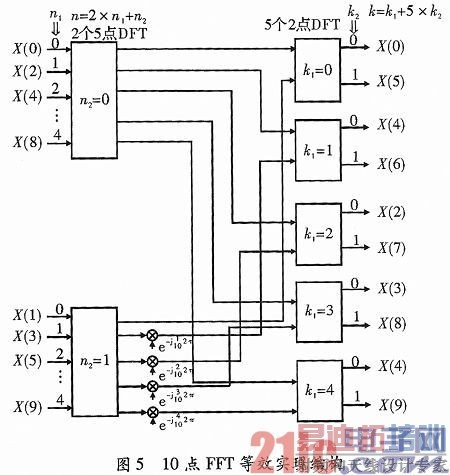

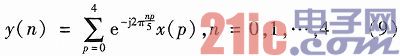

在图4中,出现了10点FFT计算,为有效节省乘法器的资源,对10点FFT计算进行变换处理,分解为5点FFT的计算。10点FFT变换可表示为式(6)

由式(8)可得,一个10点的FFT运算可等效为一级5点FFT和2点FFT的级联运算。具体实现框图如图5所示。

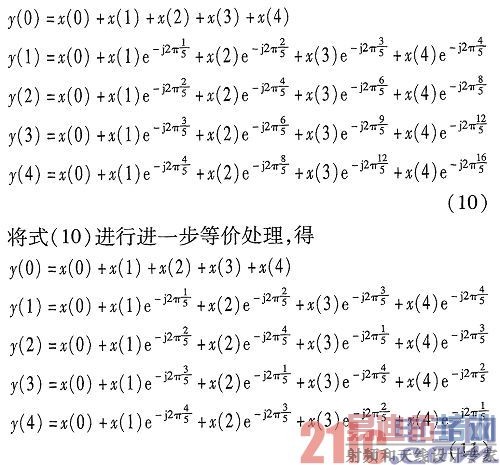

5点FFT变换可表示为

将式(9)展开,得

2 FPGA实现及测试结果

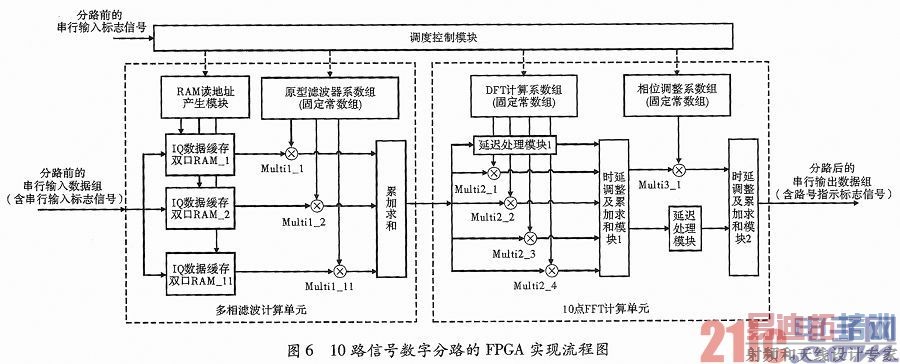

根据上述算法分析,结合FPGA资源与速度互换的处理思路,对10路信号的数字分路FPGA实现结构进行设计,具体处理流程如图6所示。

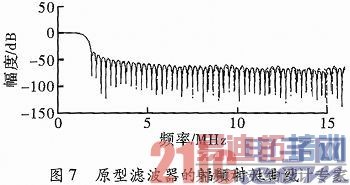

在图6中,整个10路信号数字分路模块共分为2大部分,第1部分是多相滤波计算单元,第2部分为10点FFT计算单元,两个模块在调度控制模块的控制下工作。整个模块的工作时钟fclk=96 MHz,原型滤波器选用110阶的匹配滤波器,滤波器的幅频特性曲线如图7所示。整个10点数字分路的FPGA处理流程如下。

(1)输入信号同时进入11组并行工作的RAM存储区,每进20个数据做一次流水处理,每个流水处理共有60个处理时钟,共进行5次10点FFT计算;也就是说每进20个数,输出50个数,每路5个点。

(2)调度控制模块控制11个存储RAM在每个时钟周期产生11个不同数据,同时控制原型滤波器系数组产生11个多相滤波系数,11个数据和11个多相滤波系数进行相乘及累加产生1个FFT计算输入点;每10个FFT计算输入点组成1个10点FFT计算组,并用使能信号标识,串行送给10点FFT计算单元。

(3)根据10点FFT拆分为2个5点FFT和5个2点FFT计算流程及式(11)的数学计算公式,对多相滤波计算单元串行输入的10个数据复制成相同的5组,第1组延迟4个时钟周期输出,第2~5组在调度控制模块的控制下分时乘以不同的FFT计算系数,然后对5组输出数据进行时延调整及累加求和,分别串行输出2组5点FFT计算结果;对第1组数据在调度控制模块的控制下分时乘以不同相位调整系数,对第2组延迟4个时钟周期输出;最后对2组输出数据进行时延调整及累加求和,串行输出10个FFT计算结果,并通过使能信号对10个FFT计算结果进行标识,使能信号的上升沿代表第1路数据。

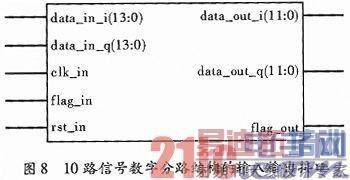

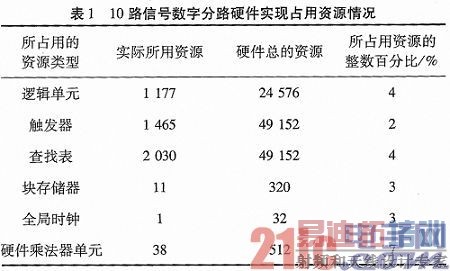

文中的10路信号数字分路结构在Xilinx的Vitex-4器件上实现,具体型号是xc4vsx55-11ff148,图8给出了10路信号数字分路的输入输出接口,表1给出了算法的硬件资源占用情况。

3 仿真验证及实际测试结果

在ISE9.2.1环境下,采用VHDL完成了10路信号的数字分路模块的开发,并采用ModeMm 6.2b软件进行仿真验证。同时,为验证设计的10路信号的数字分路模块的正确性,将10路信号的数字分路模块连同解调模块在搭建的测试系统中进行了实际测试。测试输入信号源为10路QPSK信号,10路8PSK信号以及10路16APSK信号;测试输出为10路信号的分路输出星座图及解调位同步后的星座图。图9为3种调制方式的分路输出星座图,图10为3种调制方式位同步后的星座图。

4 结束语

本文介绍了一种基于FPGA的10路信号的数字分路实现结构,在ISE9.2.1环境下,采用VHDL语言进行了实现,并在硬件平台上对分路程序的性能进行了测试。该结构能够有效降低FPGA的硬件资源消耗,尤其是乘法器的资源消耗,在全数字群解调器工程实现中有着良好的应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:用于大容量FPGA设计的EDA工具集成与远程调用

下一篇:FPGA前辈分享