- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的帧同步提取方法的研究

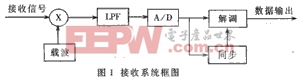

在可靠的通信系统中,要保证接收端能正确解调出信息,必须要有一个同步系统,以实现发送端和接收端的同步,因此同步提取在通信系统中是至关重要的。一个简单的接收系统框图如图1所示。

本文介绍一种基于现场可编程门阵列(FPGA)的同步方案。FPGA是与传统PLD不同的一类可编程ASIC,它是将门阵列的通用结构与PLD的现场可编程特性结合于一体的新型器件,最早由美国Xilinx公司于1985年推出。FPGA具有集成度高、通用性好、设计灵活、开发周期短、编程方便、产品上市快捷等特点,它的门数可达100万门以上。近年来,FPGA在系统的硬件设计方面得到了广泛的应用。

1 同步序列码

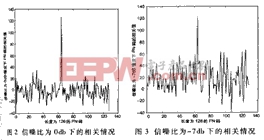

本文介绍的帧同步提取是在每一帧的前面加扩频码,该扩频码必须具有良好的自相关性和互相关特性。表1是m序列码和Gold系列码的性能比较,从表中可以看出,m序列码的自相关性和互相关特性要比Gold系列码好得多,m序列码作为同步头具有较强的抗干扰能力和较低的截获概率,而且长的m序列更容易在一定的强噪声中被提取,这样就能够充分保证数据的正常通信。因此相对于Gold系列码来说,m序列码更适合于作为同步头。本文的同步序列码指的是M序列码,M序列码是由m序列码得到的,即在相应的m序列码后补零,用以实现PN码的相等匹配,因为对应m序列码来说,1的个数总是比0的个数多一个。 利用相关法,在同步头没有来临之时,其相关峰比较低;如果数据中的同步头和本地同步头完全对齐,那么就能够出现大的相关峰值,但这个峰值可能不会达到理论值,这是因为在数据传输中,数据流包括同步头都要受到噪声的干扰。因此,同步提取还要看同步是在一个什么样的噪声环境中才能良好工作。本文介绍的是长度为128的M序列码作为同步头的同步提取方法。之所以取长度为128的PN码作为同步信息,一方面是考虑到同步提取的复杂性要求同步信息不能太长,另一方面是要满足相关峰值尽可能的大,长度为128的PN码可以提供21dB的处理增益,这使得在一定的噪声背景下仍然可以提取到相关峰值。 图2是在信噪比为0dB下的相关情况。可以看出在0dB下长度为128的M序列码作为同步头的相关特性是良好的。图3是在信噪比为-7dB的情况下做的仿真。可以发现,由噪声所产生的相关峰增高,有超过最高相关峰的趋势。经过实验,信噪比继续降低时,真正的相关峰就会被噪声所产生的相关峰淹没,这样就不能提取出相关峰。因此,同步提取要考虑噪声的影响。

[p]

2 同步提取原理

本文介绍的帧同步提取是在每一帧的前面加上长度为128位的PN码作为帧头数据(如图4所示),然后根据这些帧头数据的相关性提取相关峰值,帧头数据必须具有良好的自相关性和互相关性,当和本地码完全相同时其相关峰最大。

假设PN码为p(n),经A/D采样后第n个采样点的数据是data(n),噪声是N(n),那么data(n)和PN码之间的循环互相关函数为:

Rdp(k)=data(n)·p(k+n) (1)

式中,L是PN码的长度。当data(n)正好与PN码对齐,即data(n)=p(n)+N(n)时,有:

Rdp(k)=Σ[p(n)+N(n)]·p(k+n)

=ΣN(n)·p(k+n)+Σp(n)·p(k+n) (2)

由于N(n)与PN是互不相关的,因此(2)式的前半部分相关值很小;而对于(2)式的后半部分,当其与本地的PN码完全对应,即p(n)=p(k+n)时,Rdp(k)将得到最大相关值。对于L=128的PN码,将会有一个21dB增益的相关峰,因此可以提取到明显的相关峰。

由以上分析可以看出,在同步相关提取的实现当中要用到反向器和乘法器,电路复杂,用FPGA设计必然会占很大的资源。经过研究分析并参考其它文献资料,这里采用补码配对相减匹配滤波法,仅利用减法器和加法器即可,不仅使电路设计简单,而且使电路得到极大的优化。在同步信息的复接部分用的帧头信息是一个128位的M序列码,而在同步提取部分用的则是该序列码的镜像码。

假设帧同步复接部分的同步头M序列码是:

1000010110/0010111010/1101100000/1100110101/0011100111/1011010000/1010101111/1010010100/0110111000/1111111000/0111011110/0101100100/10000000

而同步头M序列码的镜像码则为:

00000001/0010011010/0111101110/0001111111/0001110110/0010100101/1111010101/0000101101/1110011100/1010110011/0000011011/0101110100/0110100001

对镜像之后的本地码先进行编号,按照顺序依次从1编到128。第一位数字0编为1,第二位数字0编为2,第三位数字编为3......。在镜像本地码中,第一个出现数字1的位置编号为8,第二个出现数字1的位置编号为11......。依次做以下配对:

其中的映射关系是:a→10,b→20,c→30,d→40,e→50,f→60,g→70,h→80,i→90,j→100,k→110,l→120

在同步头中,既可以用符号1表示电平系数+1,用符号0表示电平系数-1,也可以用符号1表示电平系数-1,用符号0表示电平系数+1。本文采用符号0表示电平系数+1,用符号1表示电平系数-1。

配对之后,对各个组合对应的输入移位样点数据做补码减法运算。例如在组合(1,8)中,当样点数据进入移位寄存器时,将对应移位寄存器中的并行第一位输出作为被减数,第8位输出作为减数。其它组合类似。当样点数据中的同步头完全进入移位寄存器时,那么对应并行输出的第一位应该是正值,而第8位对应的是负值。两个输出做补码相减。正值减去一个负值,输出得到一个更大的数值。这时,只有增加运算的位数,才能得到正确的运算结果。

对128个编号可以做64个配对,这就需要64个减法器。64个减法运算同时进行,有64个输出结果。然后利用32个加法器对64个数值进行加法运算。逐级进行相加运算,最后得到一个相关峰值。假设data(n)是16bit的信息数据,在逐级相加运算当中,不是直接采用这16位进行补码减法和补码加法运算,而是随着一级级的相加运算,位数也一位一位地增加。这样就优化了电路,节省了FPGA资源。

假设一个码元采样8个点,经I、Q分路(以QPSK调制为例)之后,每一正交路为4个点。相对于(1,8)配对,在第一个补码配对减法器中对应的是{t13,t1[3..0]}和{t83,t8[3..0]};相对应(2,11)配对,在电路中对应的是{t23,t2[3..0]}和{ta13,ta1[3..0]};依此类推。

下面有必要分析一下为什么要表示成{t13,t1[3..0]}的形式。在补码运算中,由0101-1101=0101+0010+0001=0111+0001可以看到0111+0001的和值是一个更大的正值,是不能用4位表示的,因为这个时候和值本应为1000,表示结果8(十进制),而在补码中却为-8。如果将补码的头一位都进行重复,使其变为5位,就可完全避免这种情况的发生。例如:

00101-11101=00101+00010+00001=00111+00001=01000

11000-00111=11000+11000+00001=10000+00001=10001 通过这样的一个变换,即不会产生溢出,也不会产生错误,保证了电路进行逐级运算的正确性。

[p]

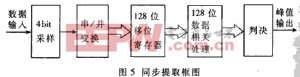

对应128长的同步头,一个码元采样8个点,经I、Q分路,每一正交路为4个点,每一路上为128×4=512个样点。采用并行处理,在数据来到之时,分成四路,每一路做一个匹配滤波器,这样可以直接由每个码元对应的样点组成匹配滤波器。将四个匹配滤波器产生的相关值比较出最大值,再和后边门限比较,超过门限,即作为同步信号。同步提取的流程如图5所示。

3 仿真结果

同步相关峰的仿真(利用Quartus2.1软件)如图6和图7所示,clk是输入时钟,in是输入数据,sclr是清零信号,out是输出信号。

用Quartus2.1软件编译适配,一片APEX EP20K400EBC652-1XEP20K400EBC652-1X只用了百分之三十的逻辑单元就可以实现同步提取。

一个完整的帧同步系统的工作状态包括两种,即捕获状态和锁定状态,并且在一定条件下使它们互相间能自动切换。当帧同步信号捕捉到时,帧同步系统应立即由捕捉状态转换到锁定状态。同步提取完成后,只是完成了初始同步,即同步捕获,还要进行同步锁定,以防止假同步和漏同步的发生。限于篇幅,这儿仅仅讨论了初始同步的实现。 通过对帧同步提取的FPGA实现可以看出,补码配对相减匹配滤波法是一个很有效的方法。它提供了一种将扩频码作为同步信息进而实现帧同步提取的方法,并且在很大程度上节约了FPGA的内部资源。这儿只是介绍了M序列码作为同步头的实现方案,对于m序列码作为同步头的实现,只要稍微做一下修改,即加一些相应的延时单元就可以实现。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于IP库的可编程器件辅助设计软件

下一篇:为系统设计人员提供的DRAM控制器