- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

半导体集成电路的发展及封装工艺面临的挑战

半导体芯片结构尺寸的缩小使得RC延迟成为制约集成电路性能进一步提高的关键性因素。转向低k铜工艺技术是业界给出的解决方案。双大马士革工艺取代了传统的铝“减”工艺,成为低k铜互连材料的标准制造工艺。

为了能与芯片制造工艺完美结合,不产生可靠性问题,低k绝缘材料必须具备一系列期望的材料特性,对低k材料研发本身的挑战在于:在获得所需要的低介电常数的同时,低k材料还必须满足良好的热和机械特性。但目前并没有完全符合这些期望特性的低k材料被制造出来,因而给半导体制造工艺带来了挑战。

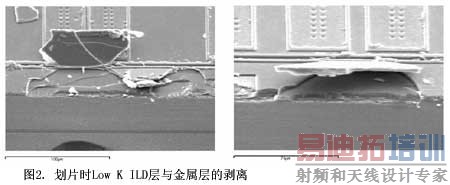

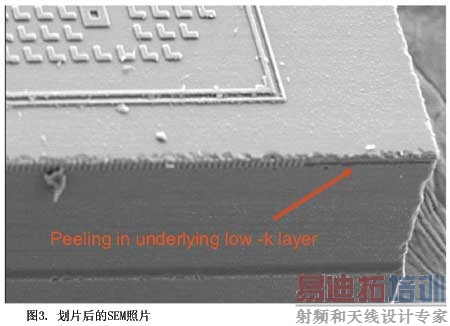

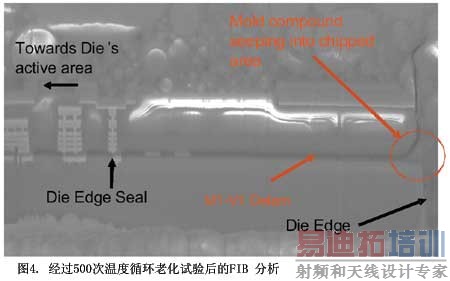

由于低k材料本身的材料特性(与金属层较弱的粘结力,较弱的机械强度),在晶片的切割时在芯片的边缘会出现严重的金属层与ILD层的分层或剥离;在焊线过程中会出现断焊,弱焊或金属层与ILD层的剥离。金铝两种材料的焊接在可靠性测试中出现比非低k材料焊线严重的金属间化合物的分层,导致集成电路电性失效。上述这些可制造性及可靠性的问题构成了对半导体封装工艺的挑战。

1 半导体集成电路的发展趋势

高速度,低成本和高可靠性代表了终端用户对半导体集成电路发展/改进的期望。而支持半导体集成电路不断改进的原动力是芯片关键尺寸的不断缩小。半导体集成电路制造产业已经成为电子制造业的基础和核心,支持并推动着相关产业的繁荣与发展。半导体工业协会(SIA Semiconductor Industry Association)在2007年2月2日的世界半导体集成电路销售调查报告中提到“全球半导体集成电路的销售额在2006年又创新高,达到2477 亿美元,比2005年的2275亿美元的销售额提高了8.9%。2006年是消费类半导体年,半导体集成电路销售额的增长主要来自流行的消费类产品,如手机,MP3播放器及高清电视等。而这些电子产品销售额的增长应归功于半导体集成电路设计/制造技术的进步以及随之而来的功能更丰富,成本更低廉的半导体集成电路的问世。

国际半导体技术发展路线图(ITRS International Technology Roadmap for Semiconductor)是由SIA出版的预测全球半导体集成电路技术发展的权威性报告[1]。 ITRS报告每两年更新一次,图1是ITRS 2005年版报告中关于DRAM和MPU技术节点(Technology Node)的发展趋势的预测。从图中可以看出,DRAM 线间距 (Half Pitch)从2001年以后,每3年改变一个技术节点,每两个技术节点,线间距降低50%。而在2001年以前,这个技术指标每两年就改变一个技术节点。MPU / ASIC的1/2 线间距一直到2004年还维持着每隔2年改变一个技术节点的能力,但在2004年以后,MPU / ASIC进步的节奏也慢了下来,变为每3年改变一个技术节点,与DRAM的发展趋势同步。

图1半导体集成电路技术节点发展路线图

表1列出了对光刻技术的需求的时间路线图,从表中也可以看出,MPU的物理栅极长度(Ph GL)自2005年以后也从每2年一个变化周期改为每3年一个变化周期,与DRAM/ MPU 1/2 线间距的变化趋势同步。

表1半导体集成电路光刻技术发展路线图

2 半导体集成电路发展的瓶颈和解决方案

集成电路元器件密度与能力的不断提高是以集成电路关键尺寸的不断缩小和芯片内信号互连布线不断复杂化,布线层数不断增加为代价的[2-3]。当集成电路的关键尺寸降到90纳米以下时,信号传输延迟,交互干扰噪声已及互连线的功率消耗等问题已成为甚大规模集成电路(ULSI)发展的阻碍。互连线尺寸因素对集成电路性能的影响可以通过对多层互连线阻容信号延迟 (RC Delay)的分析获得[4]。

假设集成电路内信号互连线的材料保持不变,则随着互连线尺寸的不断收缩,RC延迟将以互连线尺寸收缩速率的平方关系增加。在90nm技术节点,由互连导致的信号延迟已经超过了微处理器的门延迟。如果再考虑到交互干扰噪声,功率消耗问题,集成电路的整体性能会进一步下降。同时,由于器件集成度的提高,互连金属线的层数也要相应地增加,集成电路制造工艺的复杂化将会对制造良品率和制造成本产生负面影响。

为了解决上述问题,具有更低电阻率的互连金属材料和较低介电常数的层间绝缘材料被开发出来。IBM公司于1997年率先宣布低介电常数铜工艺晶片制造技术开发成功。铜金属具有比铝金属更低的电阻率(1.68μΩ.cm vs 2.65μΩ.cm),采用铜金属互连线不仅可以降低互连线的线宽,还可以降低互连线的厚度,而后者可以有效地降低同一层中互连线之间的电容,减小交互干扰噪声和电源功率消耗。铜互连导线与较低K值的层间绝缘材料的引进,有效地解决了RC延迟的问题[5]。

3 低k铜工艺对半导体封装工艺的挑战

在半导体集成电路的制造工艺中引入低介电材料和铜导线能够显著地提高集成电路的性能,但同时它也为后续的半导体封装工艺带来了诸多困难。当作为金属层间绝缘材料的二氧化硅被低介电材料(K值小于3)所取代时,新的ILD层比传统的ILD层更脆,而且具有相对较差的导热性和机械强度,与金属层的粘结力与传统的二氧化硅材料相比较小。低k材料的引入给半导体封装中的划片(Dicing Saw)和焊线(Wire Bonding)工艺带来了挑战[6]。

4 在划片工艺中金属层与ILD层的分层与剥离

在低k 晶片的划片过程中,最常见的缺陷是芯片边缘金属层和ILD层的分层(Delamination)或剥离(Peeling)。由于低k材料本身所固有的特性(如与金属层较弱的粘结力,较弱的机械强度),在低k晶片的划片过程中,经常可以在芯片边缘发现严重的金属层与ILD层的分层甚至是剥离(如图2,3所示)。这种缺陷在普通的非低k晶片的划片过程中是不存在的或是极少出现的。这种新的缺陷不仅降低了划片工序的良品率,更严重的是它会使集成电路在使用过程中产生潜在的可靠性问题(图4)。而在集成电路半导体封装的大规模生产中,对每一个芯片的切割质量进行100%

的质量检查是不可能做到的,因为受检测手段和检测时间的限制,100%的质量检查无法满足经济规模生产的要求。同时,依靠生产检查人员对已划片的芯片样品进行的抽检又不能保证发现所有的切割缺陷。因为缺少对低k晶片切割缺陷的深入理解及其与封装可靠性的关联性,以及切割缺陷在晶片上的分布规律,使得低k晶片的切割工艺的可制造性受到了关注[7]。

图2划片时LowKILD层与金属层的剥离

图3划片后的SEM照片

图4经过500次温度循环老化试验后的FIB分析

这种分层或剥离在芯片随后的使用过程中或可靠性试验中,随着工况条件的恶化而扩散,直至断裂,导致集成电路的失效。

[p]射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...