- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

系统时序试题

系统时序试题

答卷人: 得分: 折合:

一.对共同(common)时钟系统计算与判断

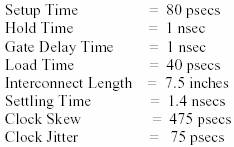

1.已知下列一些时序和传输线参数:

信号在传输线的传播延迟Tpd=168ps/inch;下面是给出的其它一些参数(和时序公式中参数的可能说法不一致,请自行分析、判断)

请根据以上条件,回答以下两个问题:

a) 系统能稳定工作的最高时钟频率大约为多少?(给出计算公式)(10分)

b) 该设计能满足器件的保持时间(Hold)的要求吗?(给出计算公式)(5分)

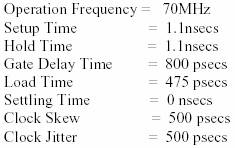

2. 已知下列一些时序和传输线参数:

信号在传输线的传播延迟Tpd=168ps/inch;

请根据以上条件,回答:

a)从时序方面考虑,保证系统正常工作的最大传输线长度是多少?(给出计算公式)。(10分)

c) 该设计能满足器件的保持时间(Hold)的要求吗?(给出计算公式)(5分)

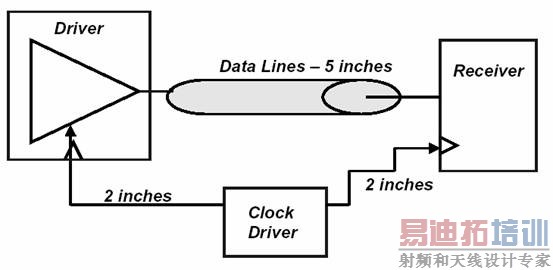

二.下面为一电路结构示意图,请检查下面的电路是否符合时序要求。

已知条件:

对于DRIVER Tco min=2.0ns Tco max=2.5ns

对于RECEIVER Setup time =500ps Hold time =300ps

对于CLOCK DRIVER Pin to pin skew =200ps Jitter=+/- 50ps

数据传输线长度为5inch 两条时钟传输线长度为2inch

传输线传输速度为200ps/inch 整个电路已经很好的匹配,没有任何反射。

试完成下面的计算。

1)电路的时钟周期最小必须满足多大?(12分)

2) 接收端的hold time 能满足这个电路的时钟周期吗?(必须通过计算来回答)(8分)

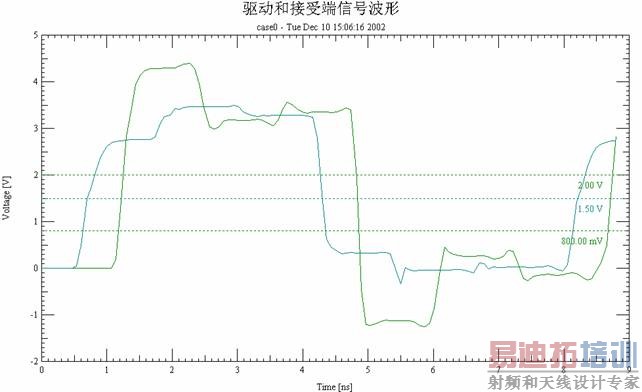

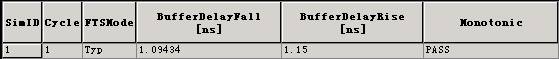

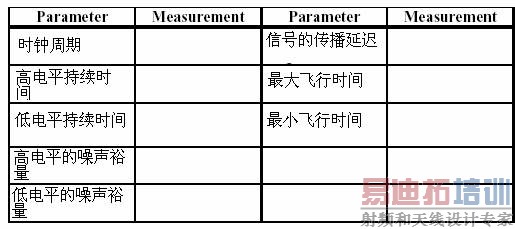

三.下图是使用Cadence SpecctraQuest的一个仿真结果,请根据信号波形图和已知的一些参数测量、计算并完成时序参数表格中的各项数据,同时回答一些问题(直接在图中测量,要求精确到0.1ns,电源电压为3.3V)。

1.时序/噪声裕量参数测量:(12分)

2.问题一:如果已知传输线的特性阻抗为60欧姆,你能估算出图中电路的电容负载大概为多大?(Tr=2.2C·Z0/2)(6分)

3.问题二:你觉得这样的接收信号有什么不足?如果需要对信号的质量进一步提高,你觉得可以采取哪些措施?(6分)

五. 请结合时序基础理论,分析一下在内存模块的设计中,随着时钟频率的提高和负载的增加,SDRAM和DDR的设计难点

我们目前可以采取哪些措施?(26分)

| 答案.rar |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...