- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于CPLD的多DSP和FPCA芯片远程更新加载设计方法

摘要:介绍了一种以CPLD为基础的对多DSP和FPCA芯片实现程序远程更新、加载的设计方法。详细分析了软硬件架构及具体实施方案,对以DSP+FPCA为架构的信号处理模块实现远程更新、加载,有重要的使用价值。

关键词:远程加载;CPLD;FPGA器件;DSP

随着硬件技术的大力发展和加工丁艺技术的不断提升,芯片技术日益成熟,软件无线电技术得到广泛应用和迅猛发展。无线电系统在整体体系结构上发生了重大变化,正沿着综合化、模块化、通用化和智能化的方向快速推进。无线电系统将模块化、标准化的硬件构成基本平台,通过软件加载技术来实现尽可能多的功能,为多种信号的功能综合和互联互通提供了技术保障。随着模块应用灵活性要求的不断增加,软件维护及升级需求的日益迫切,给软件加载技术提出了更高要求。本文提出了一种基于CPLD的多处理器远程加载管理设计应用方案,系统实现了从远端下发命令字和更新数据即可完成模块的程序更新升级和重新加载,实现软件维护和模块功能切换,满足日益复杂的系统使用要求。

1 数字处理模块

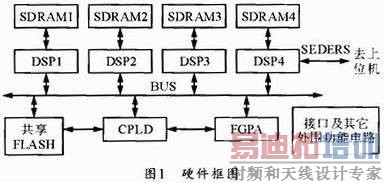

数字处理模块主要完成基带信号调制解调、RS编解码算法实现、收发通道实时控制、导航算法实现、信息层的协议实现以及大量的数据融合算法实现等。硬件设计采用了FPGA+DSP的设计构架,以1颗Altera公司的Stratix系列FPGA和4颗TI公司的DSP作为设计核心完成以上功能实现,框图如图1所示。系统要求数字处理模块要适应系统通用化和智能化的设计要求,具备远程自动更新升级、加载等功能,为系统功能多样化、维护简易化打下基础。根据系统要求和模块设计实际,结合CPLD芯片稳定性高、设计灵活的自身特点,确定采用CPLD作为整个数字处理模块的功能管理芯片,实现对整个处理模块的电源管理、状态检测、上电复位管理、各DSP及FPGA的程序加载管理、远程更新等功能处理。

当系统需要对本模块的软件进行升级或者模块功能重构时,系统将更新命令字和更新内容通过SEDERS总线下发至DSP4,再送入CPLD进行解码、识别分类,根据指令要求启动CPLD对FLASH中的相应空间进行擦除、更新操作。当操作完成后,CPLD强行启动DSP或FPCA,重新加载FLASH中的程序,完成系统软件升级或者模块功能重构任务。

2 远程更新硬件实现

远程更新和加载就是系统具有从远端通过下发指令或参数对处理模块中存储的应用程序进行修改升级的功能,模块内部控制单元启动加载模块,完成模块功能重构。反映到硬件功能就是主控芯片要具备擦除、读写模块内存储芯片的功能,可以控制模块内的各处理器及可编程器件重新加载运行新程序。数字处理模块采用4颗DSP芯片和1颗FPGA来完成系统的数据处理任务,因此在系统升级时需要对4个处理器或部分处理器及FPCA的程序进行更新并重新加载。所以主控芯片要具备擦除、读写各DSP和FPCA芯片挂接的FLASH芯片,并能对其完成程序加载。

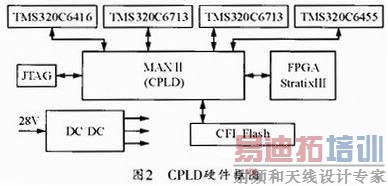

硬件设计时FLASH芯片采用了集中式设计,多个DSP芯片和FPGA分段共享同一片大容量FLASH。共享存储器有利于提高模块可靠性、模块小型化设计、有利于主控模块对其操作控制,有效降低功能实现复杂度,也有利于扩充模块功能。一般FPGA设计多采用挂接与之匹配的FLASH芯片,这些专用存储芯片不但具备专用接口与FPGA匹配,而且内部嵌入了FPCA信息,硬件设计时只需要将FPCA设计成主动加载模式即可。系统上电后FPGA将自动识别存储器并完成程序加载,整个过程不需要外部干预。但对于通用存储芯片来说FPGA是无法实现自动加载的。而且这种远程控制也是要通过外部干预来实现的,所以FPGA只能设计为被动模式,通过主控模块完成加载过程。而ALTERA公司专门研发了一款MAXⅡ系列的CPLD来实现StratixⅢ系列FPGA的加载管理CPLD硬件框图如图2所示。

2.1 通用接口存储器(CFI Flashl更新

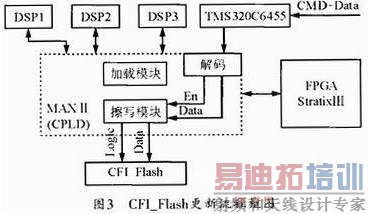

系统将更新数据从上位机下发至处理模块。经过CPLD解码、识别系统更新要求。CPLD将启动擦写模块,对CFI_Flash的相应空间段进行数据擦除操作,同时将更新数据写入存储器中,实现系统程序升级更新。其流程框图如图3所示。

2.2 程序重构

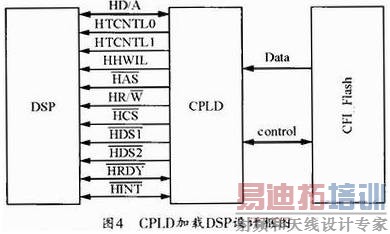

当CPLD按照系统要求将CFI Flash中程序更新完毕后,就会自动唤醒加载模块,对已更新的处理器或FPGA的程序进行重新加载。DSP的加载相对简单,将DSP设计成主机口加载模式,设计框图如图4所示。由CPLD强行复位相应DSP使其进入加载状态,然后从CFI_Flash中分别读出各DSP的目标数据,按照主机口加载时序写入DSP的内部静态存储区,加载完毕再对DSP初始化控制寄存器进行设置,完成加载过程并唤醒各DSP重新运行新程序。完成模块处理器的功能重构工作。

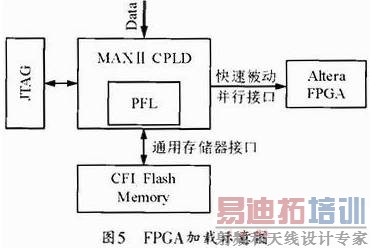

对Stratix系列的FPGA而言,加载过程相对复杂,实现起来比较困难,因为FPGA在加载过程中不仅要满足时序控制,而且加载的数据内部还含有一定的器件信息,需要满足消息格式和CRC校验才能顺利完成加载。而器件信息和CRC校验方程用户是无法得到的,因此只能采用Alte ra公司设计的MAXⅡ系列CPLD来完成加载过程。这款CPLD内部自带一个并行加载模块(PARALLEL FLASHLOADER),此模块对FPCA有专用加载接口,内部嵌入了FPGA的加载控制时序及器件信息,象一道桥梁将FPCA和通用存储器无缝连接,但硬件设计时FPGA必须设置为被动加载方式,如图5所示。系统需要对FPGA程序重构时,只需通过逻辑启动CPLD的PFL模块,PFL模块从通用存储器中读取配置数据,并且将配置数据进行格式转换打包、CRC校验后按照FPGA的加载时序写入FPGA内部,然后上拉配置完成标志位来启动新程序运行,实现FPGA的功能重构。

利用MAXⅡ系列CPLD不仅可以实现单个FPGA程序的加载,也可以根据实际应用需求通过硬件扩展以及在CPLD中增加泽码控制逻辑实现多个FPCA的加载。满足系统复杂的使用要求。

3 结束语

本设计采用MAXⅡ系列CPLD作为数字处理模块的主控芯片,来实现整个模块工作状态检测、时序管理以及多个DSP芯片和FPGA芯片的程序更新升级和加载,充分利用MAXⅡ系列CLPD芯片的硬件资源、合理调用内嵌加载逻辑模块,有效规避FPGA芯片与通用Flash芯片接口不匹配带来的设计缺陷,简化了FPGA芯片程序加载复杂度。不仅可以远程控制更新重构,还可实现动态重构,这都给处理器芯片以及FPGA芯片的加载方式和应用提出了更高的要求。

本模块已经随某通信终端完成了试飞鉴定测试,模块各项指标优异、远程更新、重构功能稳定可靠,均达到了设计要求。实现了系统模块通用化,波形功能多样化,使用维护智能化的设计要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB单面板蛇形走线布线原则

下一篇:如何找出最适合的电路板走线层数?