- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

全志平板电脑PCB设计规则一

CPU篇

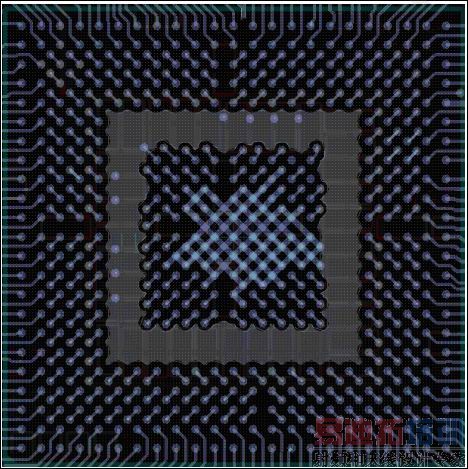

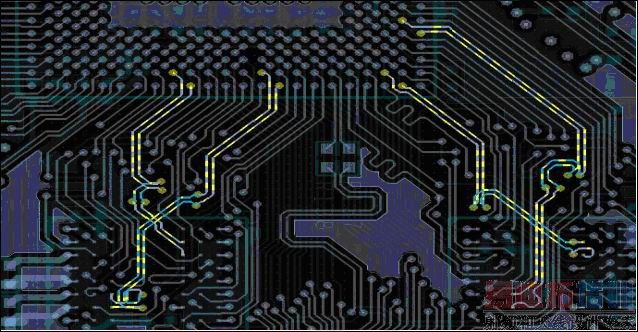

1.CPU扇出:(6 层板)外两圈采用顶层直接出线,内圈全部过孔扇出。中间的接地焊盘建议采用“井”字连接,减小过孔的阻抗。顶层用完整的地隔离开BGA信号与电源、地。

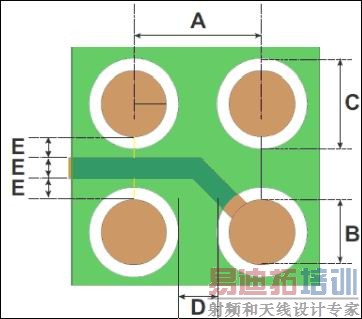

在走线前,还需要确定好 BGA走线的宽度以及焊盘和过孔的尺寸。

焊盘类型:NSMD(阻焊层比焊盘的铜箔开窗大)

焊盘间距:A 0.8mm (~31mils)

焊盘尺寸:B 0.34mm (~13mils)

阻焊开窗:C 0.44mm antipad

开窗间距:D 0.36mm

焊盘间走线:5mil 最大线宽

走线宽度:E 0.127mm (5mil)

焊盘和走线间距:E 0.127mm (5mil)

2. 电源尽量采用下图所示的电源分割方式:

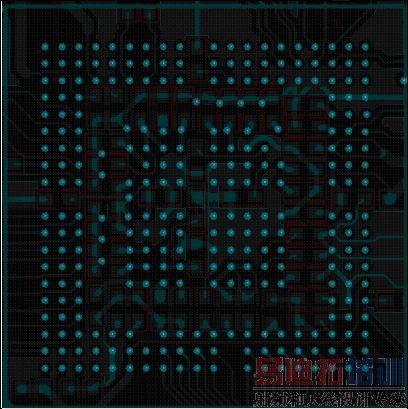

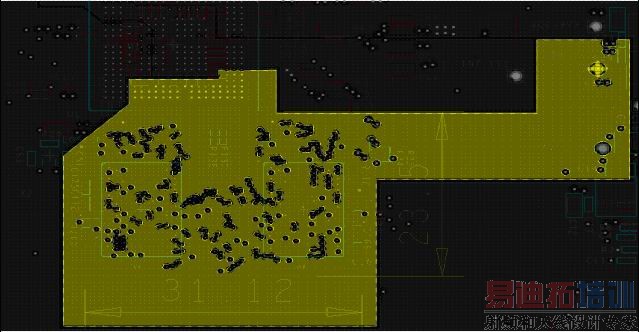

3.CPU散热:

BGA 底层的电容排列以及过孔的示意图,保证CPU 能达到良好的散热效果:

DRAM篇

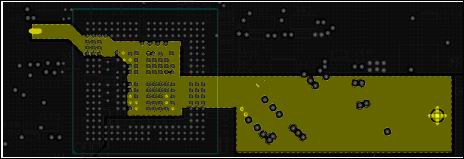

1.CPU与DDR的布局与布线。DDR的布局及布线的宽度和CPU之间的距离如下图所示:

2. 数据、地址和对应的控制信号--------需要做阻抗匹配, 单端阻抗为50 欧姆。保证所信号走线有完整的参考平面。(数据线等长,以 16 位DDR来举例:DQ[0:7]、DQS0、DQS0#、DQM0 为一组,DQ[8:15]、DQS1、DQS1#、DQM1为一组,其中DQS0-1、DQS0-1#为差分对。这 1 组里的 3 组信号是同步从CPU打出,DQS差分对是来对其他两组采样的)。

3. CPU与DDR之间的走线长度建议如下:

-DQ0-7、DQM0、DQS0 Length matching 100mil;

-DQ8-15、DQM1、DQS1 Length matching 100mil;

-DQ16-23、DQM2、DQS2 Length matching 100mil;

-DQ24-31、DQM3、DQS3 Length matching 100mil;

-DA、CONTROL、CK Length matching 300mil;

-DQSn、DQSn# Differential pairs Z0= 100 ohm,Length matching 10mil;

-CK、CK# Differential pairs Z0= 100 ohm,Length matching 10mil。

4.针对 4 片DDR的布线:

比如 CLK频率为 400MHz 时,CLK 周期为2.5ns,数据和 CLK采用“T"型拓扑布线时,为了让 T 的另一边反射回到 T 型接点时,接点信号在上升沿的时间, (周期为 2.5ns 的上升沿时间是 1/6 周期,即 0.4ns),PCB 走线6inch=1ns,0.4ns*6inch=2.4inch,算上来回时间就是,T 型右边走线的长度为:1/2*2.4ns=1.2inch;

5. 数据线同组内的排列

数据线同组内的排列可以采用任意组合进来连接,比如:DDR 的DQ0 管脚可以接 CPU的 DQ6;

6.CLK走线示意:

7. SDQ0-SDQ0#, SDQ1-SD10#, SDQ2-SDQ2#, SDQ3-SDQ3#,走线示意:

8.DDR电源:DRAM-VCC,为DDR走线提供完整的阻抗匹配的参考平面:

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...