- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

第二代高速串行总线,那些让人讨厌的问题

您可能已经拥有使用第一代串行总线技术的经验,如2.5Gbps的PCI Express和1.5 Gbps的串行ATA (SATA)等。在此基础上,采用第二代串行技术标准的产品正大量推向市场。一些工程师们甚至看的了第三代串行技术规范的设计要求,包括像 SATA3.0,传输率 可以达到

6Gbps,并且这些技术在各个标准工作组总不断演化、发展。

串行总线技术不断推进、演化,信号具有更快边沿速率和更小的单位时间间隔(UI),需要在设计、一致性测试和调试过程中考虑到很多特殊的要求。这些串行标准速度之高,使您需要考虑射频信号、传输线效应等等这些在以往低速系统中不存在的问题。

运行在下一代串行总线的系统中,电信号上的故障会比以前更加严重的影响到信号完整性和信号的质量。信号传输路径上的导体,包括电路板走线、过孔、连接器和电缆等由于回波损耗和反射等传输线效应,严重的降低信号的电平、延缓上升时间,产生更多的噪声。

Gigabit 的传输速度

随着标准定义的数传速度的不断上升,一个比特所占用的时间越来越短,传输信号和接收信号的裕量变得越来越紧张。LVDS和多电平信号更加容易受到信号完整性问题的伤害,比如延时、噪声和码间干扰(ISI)。信号对时序问题、发送端到接收端之间的阻抗、系统级软件和

硬件的交互问题更加的敏感。而多通道的结构增加了系统设计的复杂程度,增加了通道间时间延时和串扰发生的可能性。

抖动

当今的高速串行总线和嵌入式时钟系统意味着对抖动有更大的敏感性,很可能由于抖动造成误码性能的恶化。通常,抖动是由于串扰、系统噪声、同步开关输出和其他有规律发生的干扰信号所产生的。随着数据率不断上升、多通道的设计和更加紧凑的布局,使得上述这些干扰更加容易的转变为抖动。

传输线效应

信号的发送端、信号走线和接收端组成了串行数据网络。隐藏在网络下面,改变信号传输特性的因素是分布电容、电感和电阻。传输线效应随着信号速率提升而显现出来,严重的影响信号质量,并可能导致误码。

噪声

噪声是出现信号幅度上的异常电压。噪声通常来自于系统的内部和外部。外部噪声源有工频干扰,空间辐射等,内部噪声源包含数字时钟、高速芯片和开关电源。噪声可能是瞬态的,或者是宽带的随机噪声,还可以导致信号的相位出问题。就像抖动会影响信号时序一样,噪声会引起信号幅度上的异常,对系统误码率有至关重要的影响。

一致性(Compliance)测试

串行总线的一致性测试规范中,通常包括幅度、时序、抖动和眼图的测量。最新的一些串行标准更加关注扩频时钟 (SSC)、接收端灵敏度的测试,以及电缆、连接器的回波损耗和反射。对于每一种特定的标准,并不是所有的测量都是一致性测试所需要的。

测试点 (Test Point) 在标准的一致性测试或者规范本身中会定义。

眼图测量

眼图测试是一致性测试中最为关键的部分。如图 1 所示,在示波器上得到的一个串行信号的眼图。眼图测量通过从数据中恢复出的时钟进行触发,对串行信号在一个 UI 时间内多次叠加而形成。在眼图的上、中、下方各有一块测试失败区域被称之为“模板”(蓝色部分),标明了信号不能进入的禁区。眼图测试将在后面的“信号分析”部分做进一步的讨论。

图1:在示波器上进行眼图测试

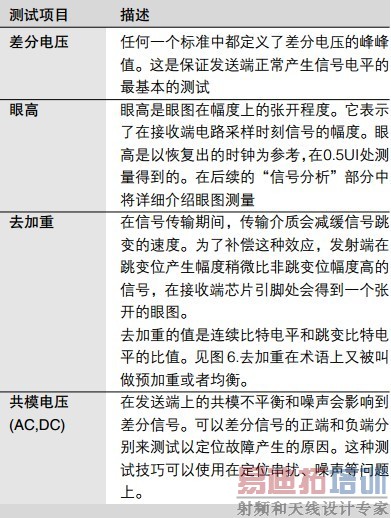

下面的列表总结了一些在插拔大会(plug-fests,验证一致性和兼容性的测试会议)中经常使用到,以及在最终产品进行一致性测试时候的测量项目。

表1:幅度测试项目一览表

幅度测试

幅度测试列举在表2中,主要是为了验证信号能否到达规定的电平并保持稳定,能在传输媒介中可靠的向接收端发送“1”和“0”。

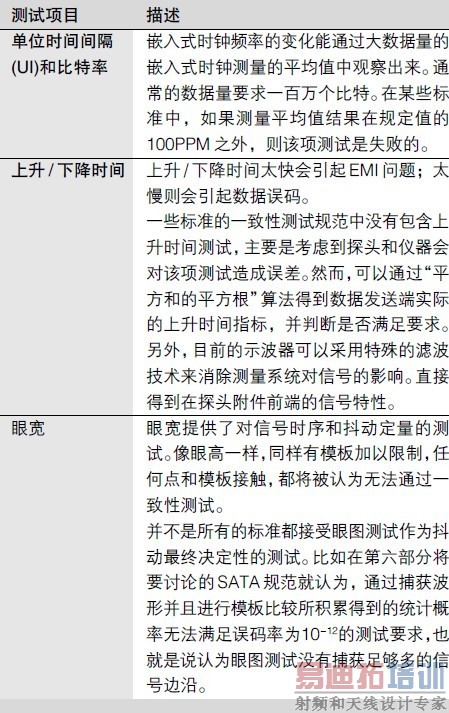

表2时序测试描述

时序测试

时序测试的项目列在表2中,主要是来验证信号是否存在异常的时序变化,是否有足够快的跳变来确保关心数据信息传输正确与否。这些测试需要高性能的测量工具来检测由于分布电容、电阻,串扰等引起异常和信号质量的恶化。

抖动测试

随着数据率不断提高,抖动问题成为了最难解决的问题之一。许多公司开发了专用的抖动分析工具,帮组工程师快速的识别产生抖动的原因以及抖动造成的结果,更好的理解抖动的复杂性。

确定性抖动和随机抖动都可以从频域角度上得到结果。为了保证兼容性,数据发送端的抖动一定不能太大,而接收端的必须要能够容忍一定量的抖动,并且能正确的进行时钟恢复(CDR)并解串行数据(De-serialize)。其他的信号特征,如幅度和上升时间,都会影响到抖动容限。实际上,抖动测试就是误码率测试。

时间间隔误差(TIE)是许多抖动测量的基础。TIE是恢复出的时钟边沿和实际波形边沿的时间差值。通过对TIE进行直方图分析和频谱分析,可以得到高级的抖动分析结果。直方图可以帮助工程师隔离由于外部其他电路,例如开关电源,所引入的抖动。

抖动测试通常需要比较长的时间,因为必须要连续的采集上亿个边沿,才能确保对10

-12误码率的准确表示。带有高速捕获速率和抖动分析工具的示波器可以大大的减

少抖动测试的时间。

更深入的抖动测量请参看“信号分析”部分。

接收端灵敏度测试

一些高速串行总线的管理机构非常关心接收端灵敏度的测试。该项测试可以证明接收芯片内部的 CDR 和解串行器件,在有外部干扰,如抖动、噪声和时序问题的环境下,能够准确的恢复时钟和数据。

电路板级互联测试

传输媒介在信号完整性中的作用越来越重要。在低成本的介质中,如 FR4 上,要设计速率超过 Gbps 的 LVDS信号,并且信号走线上有电缆、连接器等,会遇到很多布板设计以及测试上的挑战。许多的标准对介质的损耗、阻抗、串扰有着严格的要求。

时间间隔误差(TIE)是许多抖动测量的基础。TIE是恢复出的时钟边沿和实际波形边沿的时间差值。通过对TIE进行直方图分析。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB板剖制的流程

下一篇:电子产品设计中的信号完整性问题,随着速率提高日益严重。