# 深亚微米 VLSI 物理设计中天线效应的预防及修复

王伟, 冯哲, 候立刚, 吴武臣

(北京工业大学 电控学院集成电路与系统研究室, 北京 100022)

**摘要:** 深亚微米超大规模集成电路(VLSI)中金属互连线的天线效应(PAE)将会严重影响芯片物理设计的结果,甚至造成设计的失败。因此详细分析了天线效应的产生、危害和计算方法,重点讨论了深亚微米 VLSI 芯片物理设计中的 PAE 预防和修复方法,并且针对面积和时序要求苛刻的复杂芯片设计提出了优化的迭代流程。上述方法和流程成功应用于本研究室协作承担的“风芯 II 号”H.264/AVC-AVS 视频解码 SoC 芯片的后端物理设计过程中,极大地提高了天线效应的预防和修复效率,消除了版图中全部潜在高危 PAE 问题且节省了 18.18% 的迭代次数,节约了 17.39% 的芯片管芯面积,确保并实现了芯片流片的一次成功。

**关键词:** 天线效应(PAE); 深亚微米; VLSI; 物理设计; 预布线; 迭代

**中图分类号:** TN4      **文献标识码:** A      **文章编号:** 1000-7180(2007)08-0042-04

## Process Antenna Effect Avoidance and Fixing in Deep-Submicron VLSI Physical Design

WANG Wei, FENG Zhe, HOU Li-gang, WU Wu-chen

(VLSI & System Laboratory, College of Electronic Information and Control Engineering, Beijing University of Technology, Beijing 100022, China)

**Abstract:** PAE (Process Antenna Effect) is a key point in deep-submicron VLSI design due to its negative influence. This paper analyzes the inducement, the harmfulness and the relating computing methods of PAE. A practical way to avoid and to fix PAE violation in deep-submicron VLSI physical design is discussed and provided in this paper, which is used in “Phoenix II” H.264/AVC-AVS decoder SoC chip’s back-end design and ensures the success of the chip on its first tape out, with an optimized iteration flow to eliminate all of the PAE violation in chip layout much more efficiently by 18.18% less iteration times and save chip’s die area by 17.39% as well.

**Key words:** process antenna effect (PAE); deep-submicron; VLSI; physical design; pre-route; iterative

### 1 引言

金属互连线上的局部电荷累积和放电现象将严重影响芯片的物理设计结果甚至造成设计的失败。Wojciech Maly 等指出这种电荷的积累和瞬间泻放会引起栅氧化层的损伤,严重时甚至可以击穿 MOS 管的栅氧化层,造成芯片的彻底失效<sup>[1]</sup>。随着 CMOS 的制造工艺的进步,门的尺寸越来越小,金属互连的层数越来越多,发生天线效应的可能性也就越来越大。经验表明,在 0.4 μm 以上工艺条件下一般可以不用过多地考虑天线效应的影响,而到了 0.25 μm 以下的深亚微米制程精度,这种潜在的由 PAE 引起的芯片失效的危险已经不容忽略。

### 2 天线效应的产生和计算

连接到 MOS 晶体管栅极的金属层在离子刻蚀和溅射的过程中积聚了大量游离电荷,由于  $Q=CV$ ,

收稿日期: 2006-12-14

堆积的电荷便在多晶硅栅和衬底之间形成了一个偏压,直接加载在薄薄的栅氧化层上。当金属线的电位增大到足够高时,将会出现纵向穿越栅氧化层直至衬底的电荷隧穿泄放,其结果是导致栅氧化击穿电压的下降和栅氧化层的失效,甚至会直接击穿 MOS 晶体管的栅氧化层,造成器件不可恢复的失效,并大大降低 0.18 μm 工艺及以下的芯片流片时的成品率。

由于芯片制造过程中某些工艺步骤的特殊要求,部分金属导体层必须直接暴露在等离子束和 UV 光下,故无法仅仅通过工艺参数的优化而将 PAE 的负面影响彻底消除。此时金属导体层上积累的电荷的数量与其暴露部分的面积成正比,因此通常采用 Antenna Ratio 来衡量芯片中某处天线效应可能发生的几率。Antenna Ratio 是指所允许的构成“天线”的导体(一般是金属)同其所连接到的栅氧化层的面积的最大比率,即

$$\begin{aligned} \text{Antenna Ratio}(N_{ij}, G_k) &= \frac{\text{Area}_{\text{metal}}}{\text{Area}_{\text{gate}}} \\ &= \frac{\text{Area}(N_{ij})}{\sum_{G_k \in C(N_{ij})} \text{Area}(G_k)} \quad (1) \end{aligned}$$

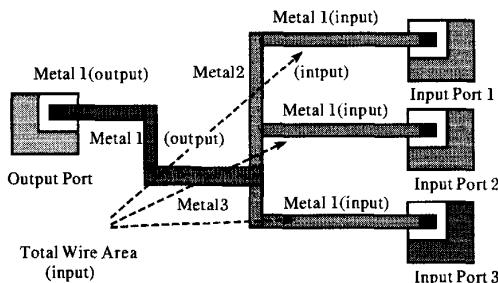

这里的导体面积  $\text{Area}_{\text{metal}}$  是指从 MOS 管的输入端开始算起, 直至到达该回路最顶层金属线之下 的所有金属互连线 ( $N_{ij}$ ,  $i$  为互连节点所属的金属层号,  $j$  为金属层上的互连节点编号) 的面积总和。在这些金属互连线上将会累积电荷并导致输入端 MOS 管栅氧化层出现可能被击穿的潜在危险。而顶层金属线之下连至输出端晶体管栅极的金属线并不会被计算在内, 这是因为在芯片的制造过程中其上多余的游离电荷可以通过低阻的输出端 MOS 管顺畅泻放。同理, 顶层金属线也不会对 AR 的值做出任何贡献, 因其最后被刻蚀完成的同时, 就标志着从输入 MOS 管到输出 MOS 管的通路正式形成, 多余的电荷此时全部可以通过输出端得到泻放。栅氧化层面积  $\text{Area}_{\text{gate}}$  则是指各个输入端口所连接到的不同晶体管 ( $G_k$ ) 的栅氧化层的面积总和。以图 1 所示的典型五层金属工艺为例 (M5 和 M6 为电源网络布线), 图中金属线 Metal 3 的实际 Antenna Ratio 值的计算公式如下:

$$\begin{aligned} \text{Antenna Ratio}_{m3} &= \frac{\sum \text{TotalWireArea}(\text{input})}{\sum \text{TotalInputPortArea}} \\ &= \frac{\sum \text{Area}_{\text{metal1}}(\text{input}) + \text{Area}_{\text{metal2}}(\text{input})}{\text{Area}_{\text{port1}} + \text{Area}_{\text{port2}} + \text{Area}_{\text{port3}}} \quad (2) \end{aligned}$$

图1 金属线 Metal3 上实际 Antenna Ratio 的计算

当某条金属互连线上实际计算出的 Antenna Ratio 大于厂家给定的最大允许 Antenna Ratio 时, 则认为此处容易发生天线效应。在基于等离子技术的 3 种不同工序中, 暴露位置的不同将造成栅氧化层的损伤几率分别正比于金属互连导体的图形面积、侧面积和通孔的总面积。因此, 通常主要分为 Partial Checking 和 Cumulative Checking 两种精度模式, 前者只考虑顶层金属线的 PAE 问题, 后者则同时考虑顶层金属线及其下各相连金属层的影响。

并将累计的 PAE 作为最终判定和检查的依据。过于保守的算法会占用过多的布线资源并降低布通率, 随着工艺技术水平的提高, 多数制造厂商要求采用 Partial Checking 模式作为折中。

### 3 天线效应的预防和消除

在芯片的后端物理设计过程中, 主要通过“改变布线方式”和“插入反偏 PAE 二极管”这两种方法来预防由于 PAE 而可能引发的芯片失效和修复全芯片详细布线后仍然存在的局部高危 PAE 问题。

#### 3.1 对版图布线方式的调整

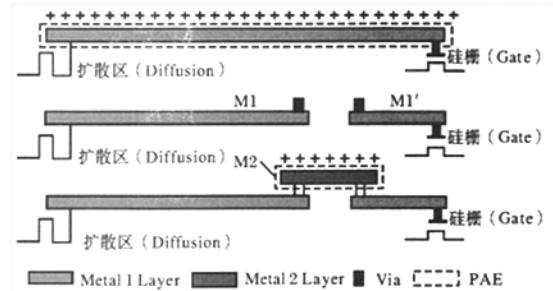

在芯片的详细布线阶段, 可以要求 router 通过“桥接”和“跳层”的方法来截断过长的金属线, 从而在离子刻蚀此金属层时(如 Metal 1 Net)达到有效减少冗长的互连导体上游离电荷的积聚数量, 降低栅氧化层上的反偏电压的目的<sup>[2]</sup>, 如图 2 所示。此时, 通过跳层的方式改变了 Metal 1 中过长的金属线的连接方式, 在靠近其远端(离硅栅比较近的一侧)添加了从 Metal 1 到 Metal 2 的通孔并形成桥接的跳线。在芯片生产过程中刻蚀 Metal 1 上的连线 M1 和 M1' 时, 由于桥接跳线 M2 尚未生成, 短线 M1' 上积累的游离电荷的数量还不足以对 MOS 管的栅氧化层构成威胁, 从而有效地预防了严重 PAE 效应的出现。当布线层所处的位置较高, 或是存在 PAE 问题的区域上层出现硬宏单元阻挡时, 亦可以选择向下“跳层桥接”的方法来达到同样的效果<sup>[3]</sup>。但是由于位置较低的金属层上的布线资源往往相对紧张, 该方法在实际中并不常用。

图2 通过“桥接”和“跳层”截断过长的金属线

在实际设计中, 在较长的金属线中插入缓冲器 (buffer)也可起到类似的“化长为短”的作用, 但这种方法会对全芯片的时序造成影响, 并不如“向上跳层桥接”和“向下跳层桥接”易于实现。而“桥接跳线”方法无疑会导致芯片全局布线阶段出现更多的跳层线条和通孔, 并在一定程度上引发布线拥塞 (congestion) 问题, 因此在芯片全局布线资源较为紧

张的情况下,单凭这种方法往往不会起到很好的效果。

### 3.2 添加反偏 PAE 二极管

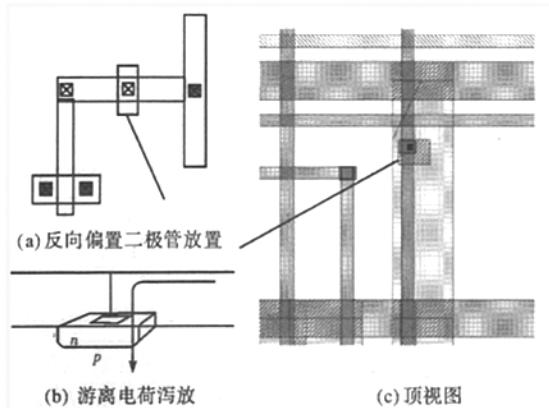

如图 3 所示,在靠近输入端 MOS 管栅极的位置放置反向偏置二极管(如图 3(a)所示),可以使金属互连导体上集聚的游离电荷经由二极管的扩散层和衬底安全泄放(如图 3(b)所示),从而有效地避免了 PAE 问题的发生。

图3 反向偏置PAE二极管的添加

PAE 二极管通常分为 N-IMP 和 P-IMP 两种,分别采用 NMOS 和 PMOS 两种工艺制成,其顶视图如图 3(c)所示。为了更为有效地起到保护作用,二极管通常采取反向偏置并尽可能地靠近输入端放置,因此并不会在芯片加工完成后给逻辑功能带来任何影响。只有当游离电荷积聚到一定程度,静电高压产生并达到二极管的反向击穿电压时,PAE 二极管才会导通并泄放电流,起到保护栅极的作用。

同 PAE 二极管相比,跳层桥接方法更容易造成更大的时序延迟并引发时序不收敛等问题,而插入二极管所引发时序延迟小到可以忽略,并且可以非常有效地用来修复跳层桥接无法满足要求处(如高层金属的 PAE 问题)的残余高危 PAE 问题。但是由于每个二极管自身固有的寄生电容结构,其不可避免地会在芯片中产生极为微小的漏电流(Leakage Current),因此当大量插入 PAE 二极管后,不仅会造成芯片面积和制造成本的增加,还会进一步增大动态功耗,影响芯片的性能。

综上,在当前工艺条件限制下,解决天线效应引起的芯片失效问题的关键在于如何更有效地减少金属互连导体上集聚的游离电荷,缓解薄栅氧化层上的静电高压。在实际的版图物理设计中,应当结合设计实际情况综合利用上述两种方法,在保证芯片性能和时序收敛的前提下,最大限度地解决万方数据

PAE 问题。

### 4 预布线阶段的 PAE 预防及修复迭代

随着 CMOS 工艺特征加工尺寸的进一步减小和芯片集成度的进一步增加,PAE 问题将会变得更加突出。利用自动布局布线工具得到的深亚微米 VLSI 芯片版图中甚至会包含成千上万个 PAE 错误,通过手工修改版图的方法将会变得异常复杂难以实现。除了制造工艺上的改良之外,还可以通过版图预布线阶段的合理迭代和处理,尽量在物理设计阶段全面预防和修复潜在的天线效应问题,提高芯片一次投片成功的概率。

#### 4.1 PAE 工艺库文件

为了更好地解决各类天线效应问题,通常在版图预布线阶段,就需要提供给自动布局布线工具一个合理的约束,进行 PAE 问题的判别和初步预防。上述约束信息主要是通过对应不同工艺制程条件下的特殊 Antenna LEF/DEF 工艺库文件以及其中定义的 PAE 关键字来实现的,以 SMIC 公司提供给设计者的 0.18 $\mu\text{m}$  工艺高密度标准单元 Antenna LEF 为例,其典型内容如下:

LAYER METAL2

Thickness 0.53;

AntennaSideAreaRatio 400;

AntennaDiffSideAreaRatio PWL((0 400) (0.202

400) (0.203 2281.2) (0.406 2362.4));

END METAL2

自动布局布线工具主要通过对上述特殊 PAE LEF/DEF 中定义的各类 Antenna Ratio 来识别冗长金属互连线、标准单元引出端和通孔等处的潜在高危天线效应问题,当其发现某处的 AR 阈值高于 PAE 工艺库文件中所限定的最大 AR 阈值后,就会自动尝试优先通过换层、调整布线及连接方式等方法进行修复,直到最终布线尽可能满足要求为止。

#### 4.2 PAE 问题预防/修复迭代流程及预布线流程优化

然而,随着设计规模、系统复杂度和时钟频率的不断增加和提高,布线资源趋于紧张,PAE 修复和时序收敛的兼顾难度亦随之加大,仅仅依靠软件在全局布线阶段的自动预防已难以取得很好的效果。此时通过经典的“跳层桥接”的方法来进行 PAE 问题的消除时,由于布线资源已经捉襟见肘,布线后版图中仍然会残留相当数量的天线效应问题无法消除。在这种情况下,可以通过上述“添加 PAE 反

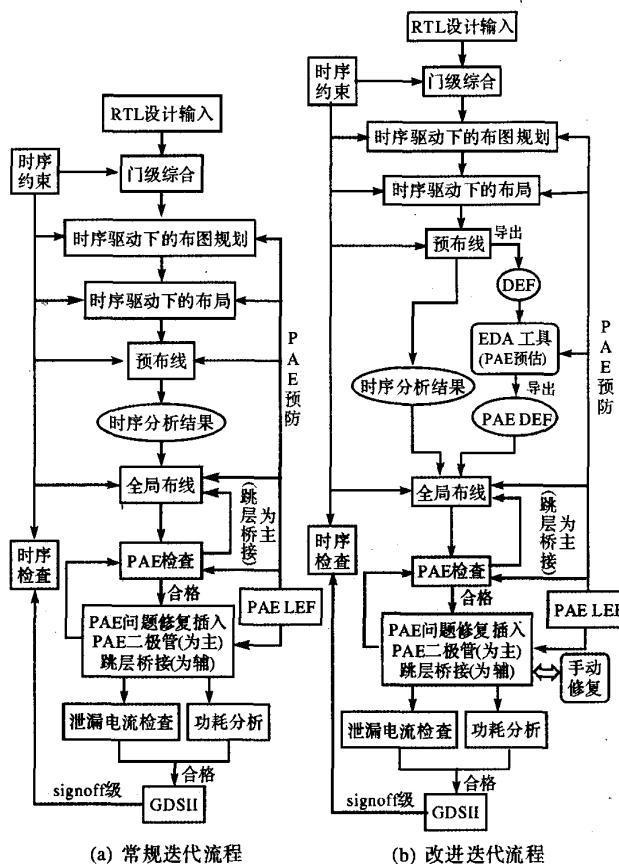

偏二极管”的方法来进一步修复残余的天线效应问题,必要时甚至还要在局部小范围内采用同软件相结合的手工修复的方法,其常规修复迭代流程如图4(a)所示。

图4 PAE问题预防/修复流程及预防布线流程优化

通常,全局布线完成后,可以在存在PAE问题的长金属线上有针对性的接入反偏PAE二极管(靠近输入端口)以修复残余天线效应问题。但是对于某些布线资源和时序要求非常紧张的设计而言,全局布线后仍需要在版图中插入大量的PAE二极管才能够完成天线效应的修复,此时用于连接PAE二极管的金属走线会在芯片中引入一定程度的拥塞,给随后的全局布线调整带来很大困难,甚至无法完成全部所需的PAE二极管的添加。这就要求IC设计者在版图的预布线阶段就要综合考虑到PAE问题的潜在影响,编写和采用适当的PAE LEF文件,并通过相应的EDA工具进行PAE预估并根据预估结果(PAE DEF形式)指导随后的全局布线。针对这种颇具挑战性的设计,文中对上述迭代流程进行了优化,其改进流程如图4(b)所示。图中的PAE DEF是指根据预布线情况的预估,含有PAE二极管插

入信息的设计交换文件(Design Exchange File)。

## 5 试验数据和结果比较

文中所采用的设计实例是本研究室协作承担的“风芯II号”H.264/AVC-AVS视频解码SoC芯片,其后端物理设计主要基于Cadence SoC Encounter数字IC设计平台,并采用SMIC 0.18μm高密度标准单元工艺库。全芯片规模在300万逻辑门左右,包含有第三方的PLL和近130个存储器模块,芯片面积要求和系统时序约束相对紧张。为了节省面积并考虑到时序约束,整个设计已经被打平,最终的布局布线由时序驱动<sup>[4,5]</sup>。

在采用了合适的PAE工艺库的前提下,首先采用如图4(a)所示的常规流程进行芯片的自动布局布线和天线效应的预防及修复,并对修复结果采用Calibre实体验证工具进行天线效应的检查,发现全局布线后仍然存在相当数量的PAE问题,预防/修复效果同预期有较大差距。随后结合此SoC芯片实际,采用如图4(b)所示的改进迭代流程,通过Cadence WROUTE在预布线阶段进行PAE预估并根据预估结果(PAE DEF形式)指导随后的全局布线。优化流程主要通过时序约束确定布线的优先级,并结合预布线PAE预估结果,遍历网表中的包括预估的PAE保护二极管在内的全部单元,结合Cadence NanoRoute纳米布线器进行详细的全局布线。对于全局布线后仍然存在PAE问题的金属互连线,则主要通过动态地插入PAE反偏二极管来进行修复。

通过对PAE预防/修复流程的改进,在满足系统时序的前提下,使得全局布线后的芯片总互连金属线长减小4.62%,通孔数目减少11.37%,消除了版图中全部的PAE预留拥塞,并进一步导致全芯片的平均漏电流功耗减小2.98%,平均功耗降低3.34%。同时进一步在版图中添加PAE反偏二极管242个并完成合理的布线及连接,最终残余PAE问题仅为5处。结合全定制版图软件进行手工交互修复,最终成功消除了金属线上的全部潜在天线效应问题。该优化迭代流程极大地提高了PAE预防/修复效率并在全局详细布线阶段节省了约18.18%的迭代次数。此外,在实际物理设计过程中,在不引起任何额外布线拥塞、时序下降和芯片性能下降的情况下,达到同样的PAE修复效果(完全修复全部PAE问题),采用图4(b)所示改进流程实际可以节省约17.39%的芯片管芯面积。

(下转第48页)

指数性增加,而文中算法计算时间极少,而且曲线十分平缓,因此,当N值越大时,文中算法的优越性越高。

(2)由图3、图4可以看出,双环网络 $G(N;1,s)$ 的直径 $d(N;1,s)$ 以s的中心对称分布,并且直径皆大于或等于 $lb(N)=\lfloor \sqrt{3N} \rfloor -2$ ,当直径等于时,即为紧优。当N为奇数时, $s=(N+1)/2$ 是中心,直径 $d(N;1,s)$ 在 $s=2,(N+1)/2,N-1$ (即最左端,中间点,最右端)取得最大值 $(N-1)/2$ ;当N为偶数时, $s=N/2$ 和 $(N/2)+1$ 两点是中心,直径 $d(N;1,s)$ 在 $s=2,N/2,(N/2)+1,N-1$ (即最左端,中间两点,最右端)取得最大值 $N/2$ ;这是由双环网络自身的对称性决定的。在特定N值时,对任何 $s_1+s_2=N+1$ ,则有 $d(N;1,s_1)=d(N;1,s_2)$ ,因此对任何N,其紧优、几乎紧优和k紧优双环网络是成对出现。

## 5 结束语

文中提出了一种双环网络 $G(N;1,s)$ 的改进直径求解算法,并利用C#语言成功实现,实验结果表明该算法相对于文献[1]算法,极大地提高了计算速度。如何利用此改进算法继续分析紧优双环网络的分布特点及研究无向单位步长双环网络 $G(N;\pm 1,s)$ 的直径求解算法是下一步研究的重点。

(上接第45页)

## 6 结束语

文中详细分析了VLSI天线效应的产生、危害和计算方法,并充分考虑到天线效应在深亚微米VLSI芯片后端物理设计中的影响,重点讨论了物理设计中的PAE修复方法和迭代流程。针对芯片面积和时序要求苛刻的特殊复杂芯片设计,进一步提出了优化和改进的PAE的预防/修复迭代流程。在保持芯片性能满足要求和系统时序收敛的前提下,极大地提高了天线效应的预防和修复效率并节省了迭代次数,节约了芯片面积。该优化迭代流程成功应用于本研究室协作承担的“风芯II号”H.264/AVC-AVS视频解码SoC芯片的后端物理设计过程中,消除了版图中全部的潜在天线效应问题,顺利地通过了投片前的各项严格检查测试,有力地确保并实现了芯片最终流片的一次成功。

## 参考文献:

- [1] Maly W, Ouyang C, Ghosh S, et al. Detection of an anten-

## 参考文献:

- [1] 方木云. 双环网络 $G(N;1,s)$ 的直径求解算法与实现[J]. 微电子学与计算机, 2005, 22(1): 58~61

- [2] 刘换平, 杨义先, 胡铭曾. 最优双环网的构造[J]. 系统工程理论与实践, 2001, 21(12): 72~75

- [3] 李乔, 徐俊明, 张忠良. 最优双环网络的无限族[J]. 中国科学, A辑, 1993, 23(9): 979~992

- [4] 徐俊明. 计算机互连双环网络的最优设计[J]. 中国科学, E辑, 1999, 29(3): 272~278

- [5] 徐俊明. 2紧优双环网络无限族[J]. 高校应用数学学报, A辑, 2000, 15(2): 148~152

- [6] 徐俊明, 尹治军. 7类新的2紧优双环网无限族[J]. 中国科学技术大学学报, 2002, 32(4): 399~402

- [7] Chen C Y, Hwang F K. Equivalent nondegenerate l-shapes of double-loop networks [J]. Networks, 2000, 36: 118~125

- [8] Chen C Y, Hwang F K. Equivalent l-shapes of double-loop networks for the degenerate case [J]. Journal of Interconnection Networks, 2000, 1: 47~60

## 作者简介:

邹伟鹏 男,(1979-),硕士,讲师。研究方向为信号与图像处理。

na effect in VLSI designs [J]. IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 1996 (11): 86~94

- [2] Chen P H, Malkani S, Peng C M, et al. Fixing antenna problem by dynamic diode dropping and jumper insertion [J]. IEEE 2000 First International Symposium on Quality Electronic Design, 2000 (3): 275~282

- [3] 杨旭, 黄令仪, 叶青, 等. 深亚微米设计中天线效应的消除[J]. 半导体学报, 2004, 25(7): 879~883

- [4] 吴伟贤, 周剑扬, 许伟坚, 等. 基于硅虚拟原形的RISC CPU核物理设计 [J]. 微电子学与计算机, 2005, 22(3): 162~169

- [5] 杨依忠, 胡永华, 尹勇生, 等. PC和SE有效结合的一种设计新方法[J]. 微电子学与计算机, 2004, 21(6): 182~184

## 作者简介:

王伟 男,(1982-),硕士研究生。研究方向为专用集成电路设计及VLSI后端物理设计。

## 如何学习天线设计

天线设计理论晦涩高深，让许多工程师望而却步，然而实际工程或实际工作中在设计天线时却很少用到这些高深晦涩的理论。实际上，我们只需要懂得最基本的天线和射频基础知识，借助于 HFSS、CST 软件或者测试仪器就可以设计出工作性能良好的各类天线。

易迪拓培训([www.edatop.com](http://www.edatop.com))专注于微波射频和天线设计人才的培养，推出了一系列天线设计培训视频课程。我们的视频培训课程，化繁为简，直观易学，可以帮助您快速学习掌握天线设计的真谛，让天线设计不再难…

---

### HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书，课程从基础讲起，内容由浅入深，理论介绍和实际操作讲解相结合，全面系统的讲解了 HFSS 天线设计的全过程。是国内最全面、最专业的 HFSS 天线设计课程，可以帮助你快速学习掌握如何使用 HFSS 软件进行天线设计，让天线设计不再难…

课程网址: <http://www.edatop.com/peixun/hfss/122.html>

---

### CST 天线设计视频培训课程套装

套装包含 5 门视频培训课程，由经验丰富的专家授课，旨在帮助您从零开始，全面系统地学习掌握 CST 微波工作室的功能应用和使用 CST 微波工作室进行天线设计实际过程和具体操作。视频课程，边操作边讲解，直观易学；购买套装同时赠送 3 个月在线答疑，帮您解答学习中遇到的问题，让您学习无忧。

详情浏览: <http://www.edatop.com/peixun/cst/127.html>

---

### 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程，培训将 13.56MHz 线圈天线设计原理和仿真设计实践相结合，全面系统地讲解了 13.56MHz 线圈天线的工作原理、设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体操作，同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过该套课程的学习，可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹配电路的原理、设计和调试…

详情浏览: <http://www.edatop.com/peixun/antenna/116.html>

---

## 关于易迪拓培训:

易迪拓培训([www.edatop.com](http://www.edatop.com))由数名来自于研发第一线的资深工程师发起成立，一直致力于专注于微波、射频、天线设计研发人才的培养；后于 2006 年整合合并微波 EDA 网([www.mweda.com](http://www.mweda.com))，现已发展成为国内最大的微波射频和天线设计人才培养基地，成功推出多套微波射频以及天线设计经典培训课程和 **ADS**、**HFSS** 等专业软件使用培训课程，广受客户好评；并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书，帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司，以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

## 我们的课程优势:

- ※ 成立于 2004 年，10 多年丰富的行业经验

- ※ 一直专注于微波射频和天线设计工程师的培养，更了解该行业对人才的要求

- ※ 视频课程、既能达到了现场培训的效果，又能免除您舟车劳顿的辛苦，学习工作两不误

- ※ 经验丰富的一线资深工程师主讲，结合实际工程案例，直观、实用、易学

## 联系我们:

- ※ 易迪拓培训官网: <http://www.edatop.com>

- ※ 微波 EDA 网: <http://www.mweda.com>

- ※ 官方淘宝店: <http://shop36920890.taobao.com>