# 数字锁相环 ISP 设计

# passmatlab

# §3.1 数字锁相环原理

模拟锁相环路(APLL)已在模拟和数字通信已经无线电电子学领域获得极为广泛的应用。随着大规模、超高速数字集成电路的发展以及计算机的普及运用,为研究和制作全数字锁相环路(ADPLL)提供了极为有利的条件。数字锁相环是在模拟锁相环的基础上发展起来的。开始,只是把模拟环路的部分数字化,后来才出现了全数字锁相环路。所谓全数字化,就是环路部件数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环。目前,全数字锁相环路的研究日趋成熟,并已制成全数字化锁相环路 FSK 信号解调器、PSK 信号解调器、位时钟提取器及同步载波提取器等。全数字化锁相环的共同特点是:

- 1. 电路完全数字化,使用逻辑门电路和触发器电路。系统中只有"导通"和"截止"两种工作状态,受外界和电源的干扰的可能性大大减小,电路容易集成,易于制成全集成化的单片全数字锁相环路。因而系统的可靠性大大提高。

- 2. 全数字锁相环路还缓和或消除了模拟锁相环路中电压控制振荡器(VCO)的非线性以及环路中使用运算放大器和晶体管后而出现的饱和及运算放大器和 鉴相器的零漂等对环路性能的影响。

- 3. 数字锁相环路的环路部件甚至整个环路都可以直接用微处理机来模拟实现。

- 4. 全数字锁相环路中,因模拟量转变为数字量所引入的量化误差和离散控制造成的误差,只要系统设计得当,均可以被忽略。

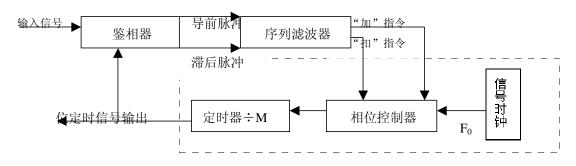

图 3.1 DPLL 的基本结构

数字锁相环的实现方法是多种多样的,数字锁相环按照数字鉴相器的形式可以分成四类,它们分别是:

## 一. 过零型数字锁相环路

这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行 A/D 变换,得到数字相位误差信号输出。

#### 二. 触发器型数字锁相环路

这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置"0"和置"1"的时间间隔内,得到相位误差信号。置"0"和置"1"的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

#### 三. 导前-滞后型数字锁相环路

这种数字锁相环路采用的鉴相器是导前-滞后型数字鉴相器。导前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。然后将误

差相位的超前或滞后信息送到序列滤波器,产生对 DCO 的"加"或"扣"脉冲控制指令去改变 DCO 的时钟周期,使本地估算信号的相位输入信号相位靠拢。四. 奈奎斯特速率采样型数字锁相环路

在这种数字锁相环路中,对输入信号的采样按奈奎斯特速率进行。也就是说,对输入信号进行 A/D 变换的采样频率必须按奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。A/D 变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

直接从接受数据流中提取位时钟信号的全数字锁相环路,在数字(数据)通信中有着广泛的应用。本课题主要是设计这种提取位时钟信号的 DPLL。我采用的是导前-滞后型数字锁相环(LL-DPLL)。LL-DPLL 位时钟提取环路的原理框图如下所示:

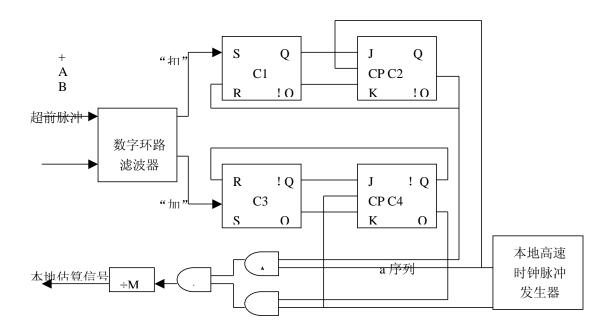

图 3.2 LL- DPLL 位同步提取器

LL- DPLL 由五部分组成:两电平量化鉴相器,序列滤波器,相位控制器,本地信号时钟和定时器。两电平量化鉴相器输出导前或滞后脉冲,它的具体可以用微分型也可以用积分型导前-滞后鉴相电路。鉴相器输出的导前-滞后脉冲经序列滤波器的过滤后输出"加"脉冲指令或"扣"脉冲指令。它的 DCO 由本地信号时钟、相位控制器和定时器构成频率稳定的本地信号时钟输出一频率 F<sub>0</sub>的脉冲序列,在未经控制的情况下,该序列经 M 次分频后得到频率 F<sub>0</sub>/M 的信号。F<sub>0</sub>/M 约等于输入信号的码速率。除 M 定时器的输出信号与输入的二进制数字信号通过鉴相器进行相位比较。鉴相器输出表征输入信号是导前还是滞后与 DCO 输出位同步信号的导前脉冲或滞后脉冲。再经过序列滤波器过滤后变为"加"脉冲指令或"扣"脉冲指令,去控制本地信号时钟序列"加"入一个脉冲或"扣"除一个脉冲,从而改变分频器(定时器)输出的脉冲信号相位。经环路的反复调整,就可以得到较为准确的位同步信号。

# §3.2 数字鉴相器的设计

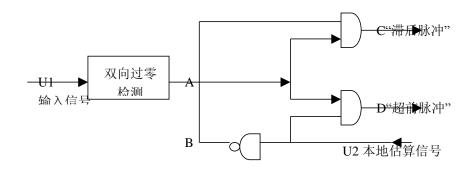

数字鉴相器也称采样鉴相器。在位同步的 DPLL 里设计的数字锁相环是采用导前-滞后型数字鉴相器,它输出一个表示本地估算信号导前或滞后于输入信号的量。如果本地估算信号超前于输入信号,则输出"超前脉冲",以便利用该"超前脉冲"控制本地估算信号的相位推后。反之,则输出"滞后脉冲",并使本地估算信号的相位前移。导前-滞后型数字鉴相器可分为微分型和积分型两种。我设计的是微分型导前-滞后型数字鉴相器。图 3.3 是微分型导前-滞后型数字鉴相器的原理图。

图 3.3 微分型导前-滞后型数字鉴相器的原理图

从图中可以看出,当本地估算信号超前于输入信号时,鉴相器输出超前脉冲(图中 D 点)。反之,本地估算信号滞后于输入信号时,鉴相器输出滞后脉冲(图中 C 点)。这里需要说明的是,输入信号是一个二进制的码流,T1 是码流的一个码元宽度,而本地估算信号 U3 是位时钟信号,T2 是该为时钟信号的周期。故导前\_滞后型数字锁相环通常只用在数据传输中,在接受到的二进制随机码流中提取位时钟信号。鉴相器用 VHDL 语言实现如下:(没有提供-passmatlab)

# §3.3 数字滤波器的设计

在数字锁相环路中,环路滤波器通常使用数字滤波器。数字环路滤波器在环路中对输入噪声起抑制作用,并且对环路的矫正速度起调节作用。数字环路滤波器具有独特的结构。导前-滞后型数字锁相环,它使用的数字环路滤波器是独特的,即"序列滤波器"。

序列滤波器又称时序滤波器。这种滤波器专门用于鉴相器输出的导前或滞后脉冲的情况。通常有两种形式: (1) 随机徘徊序列滤波器。(2) 先 N 后 M 序列滤波器

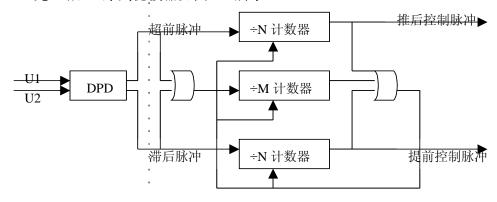

先 N 后 M 序列滤波器如图 3.4 所示。

图 3.4 先 N 后 M 序列滤波器

它的工作原理是,超前或滞后脉冲由鉴相器分别送入各自的计数器里计数,两个计数器的计数容量均为 N。而它们的和(或门输出)在计数容量为 M 的计数器里计数。 M 和 N 有下列关系: N<=M<=2N。三个计数器中任何一个计数器计满时,都会输出一个脉冲,将所有三个计数器均置"0"。当超前脉冲先(或与 M 计数器同时)计满时,表明超前脉冲多于滞后脉冲。这时,滤波器输出推后控制脉冲。在滞后脉冲多于超前脉冲时,则滞后脉冲计数器先(或与 M 计数

器同时)计满。这时,滤波器输出提前控制脉冲。假如 M 计数器在两个 N 计数器计满之前就计满数了,则滤波器既没有推后控制脉冲也没有提前控制脉冲输出,只是将三个计数器均置"0",重新开始计数.这种情况说明环路已进入同步状态,相位误差很小,并只是在导前和滞后两中状态间来回抖动。同理,噪声引起的超前脉冲和滞后脉冲的出现也是等概率的。这时,滤波器不输出控制脉冲,即不对本地估算信号的相位做调整控制。

图 3.5 设计的先 N 后 M 序列滤波器

这里 M 的取值范围是: 0<M<2<sup>5</sup>-1,N 的取值范围: 0<N<2<sup>4</sup>-1。由于 N 计数器和 M 计数器的设计差不多,所以这里只写出 M 计数器的程序为: (没有提供-passmatlab)

# §3.4 数控振荡器的设计

数控振荡器 (DCO),又称为数字钟。它在数字锁相环路中所处的地位相当于模拟锁相环路中的电压控制震荡器。但是,它的输出是一脉冲序列,而该输出脉冲序列的周期受数字环路滤波器送来的校正信号控制。其控制特点是:前一采样时刻得到的校正信号将改变下一个采样时刻的脉冲时间位置。

在导前-滞后型全数字锁相环中使用数控振荡器是"加"、"扣"脉冲式 DCO。如果数字鉴相器每一个鉴相周期输出本地估算信号是超前或滞后于输入信号的信息,经数字环路滤波器过滤后,输出"加"脉冲或"扣"脉冲指令,用此控制脉冲去控制 DCO 的输出相位。在本地估算信号超前于输入信号时,"扣"脉冲控制的结果,使本地高速时钟序列中的某一个(或几个)脉冲被扣除,被扣除一个(或几个)脉冲的受控本地高速时钟序列经除 M 分频后,得到相位推后了的本地估算信号。反之,当本地估算信号滞后于输入信号时,"加"脉冲控制的结果是在本地高速时钟脉冲序列中塞入一个(或几个)脉冲,经除 M 分频后得到相位提前了的本地估算信号。如果数字环路滤波器既没有"扣"脉冲又没有"加"脉冲控制信号输出,那么,本的高速时钟脉冲序列将不受控制,经除 M 分频后的输出本地估算信号相位和输入信号相位处于同步状态(锁定状态)。

控制器对"加","扣"指令脉冲的宽度有严格的要求。假如其宽度小于 T0,则有可能产生漏控。而如果其宽度大于 T0,则有可能会发生一次控制"加"或"扣"两个甚至两个以上脉冲的情况。从而导致同步精度变差。为了保证"加","扣"指令脉冲的宽度严格等于 T0,需要在数字环路滤波器和控制器之间附加一个控制脉冲变换电路。

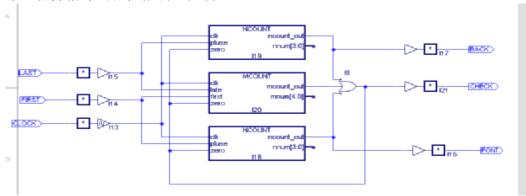

本设计中采用的 DCO 即为如下方式:

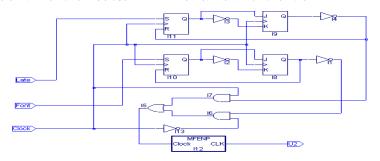

图 3.6 控制脉冲变换电路

控制脉冲变换电路一共有四个触发器组成。C1, C3 为 R-S 触发器; C2, C4 为 J-K 触发器。起始时,它们均处于"0"状态。触发器 C2 的非 Q 端使与门 A 为常开门,触发器 C4 的 Q 端保证与门 B 为常闭门。R-S 触发器 C1, C3 的状态决定着 J-K 触发器 C2 和 C4 的激励条件。以便保证在数字环路滤波器既没有"加"指令脉冲又没有"扣"指令脉冲时,触发器 C2 和 C4 在 CP 脉冲作用下不使其状态反转。触发器 C2 的 CP 脉冲是本地高速时钟脉冲发生器输出的 A 序列脉冲,C4 的 CP 脉冲是 B 序列脉冲。

当本地估算信号超前于输入信号时,数字环路滤波器有"扣"指令脉冲输出,触发器C1的状态反转至"1"状态。从而改变了J-K 触发器C2的触发条件。下一个A序列脉冲在通过与门A的同时,其后沿促使C2反转至"1"状态。触发器C2的非Q端为"0",将常开与门A关闭,同时,触发器C2的非Q端又反馈去控制R-S 触发器C1的R端,使C1置"0"。这样,又改变了J-K 触发器C2的激励条件。当A序列脉冲的下一个脉冲到来时,因为与门A已被关闭而不能通过,它的后沿又使J-K 触发器C2翻转为"0"状态。触发器C2的非Q端使与门A重新开启。因此,加到常开与门A的"扣"指令脉冲宽度(即关闭时间)严格地等于T0,保证了一次控制能准确地扣除A序列脉冲中的一个脉冲。同理,也可以保证"加"指令脉冲宽度(常闭与门B的开启时间)严格地等于T0,保证能准确地一次放行B序列中的一个脉冲,并将其塞入A序列两个相邻脉冲的中间。

图 3.7 设计的数控振荡器

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(www.mweda.com),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

## 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

## ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程, 共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS, 迅速提升个人技术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

## HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅…

课程网址: http://www.edatop.com/peixun/hfss/11.html

## CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送3个月免费学习答疑…

## HFSS 天线设计培训课程套装

套装包含6门视频课程和1本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

## 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了13.56MHz线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

## 我们的课程优势:

- ※ 成立于 2004年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

## 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

易迪拓信训 官方网址: http://www.edatop.com