# 史密斯(Smith)圆图的應用與阻抗整合

#### 前言

印刷電路板的 pattern 線路有很多必需是借助 thruogh hole 完成線路路徑的佈局, 對低頻電路而言 thruogh hole 幾乎不會對該電路產生不良影響,不過高頻電路的阻抗 (impedance) 整合卻扮演關鍵性角色,換言之若將具有 thruogh hole 的線路當作一般傳輸線路處理,就會面臨許多超乎預期的困擾,主要原因是在傳輸線路上如果設有 thruogh hole,該部位就會產生非連續性點阻抗,而該點或多或少會形成反射波,最後造成電路誤動作,類比電路的精度發生誤差等嚴重後果。

該反射波的反射程度是用反射係數表示,它是用複素數處理變成複素量。雖然電子電路經常使用複素數與 admittance等計算方式,不過實際上複素數計算相當煩瑣,其中傳輸線路與高頻電路常用的複素數計算, 如果改成史密斯特性圖表(Smith chart)方式,就可輕鬆獲得相同的計算結果。有鑑於此,本文將介紹史密 斯特性圖表(Smith chart)使用上必需注意的事項。

## 反射係數

反射係數是表示整合狀態的尺度,反射係數是負載阻抗與傳輸線路特性阻抗Z。相異時,部份入射電力未被 負載吸收,變成反射電力折返信號源時,入射電力與反射電力的比亦即反射係數可由下式求得:

Γ=反射波/入射

$$= \frac{(Z_R - Z_O)}{(Z_R + Z_O)} \psi$$

$$\cdots = |\Gamma|^{e^{i\theta}} - \cdots - (1)$$

也就是說反射係數是具有大小與位相的量,它可由上式 $Z_{R}$ 與  $Z_{0}$ 兩個阻抗關係求得,此外式(1)可轉換成下式:

$$Z_R = Z_O \times \left[ (I + \Gamma)/(1 - \Gamma) \right] - \cdots - (2) + C$$

#### 【試算例1】

假設傳輸線路特性阻抗  $Z_0$ 為  $50\,\Omega$ ,負載阻抗分別是  $0\,\Omega$ 、 $50\,\Omega$ 、 $1k\,\Omega$ 、 $j50\,\Omega$ 時,反射係數  $\Gamma$  =0.  $5\,\angle$   $45^\circ$ ,試算負載阻抗 $Z_R$ 。

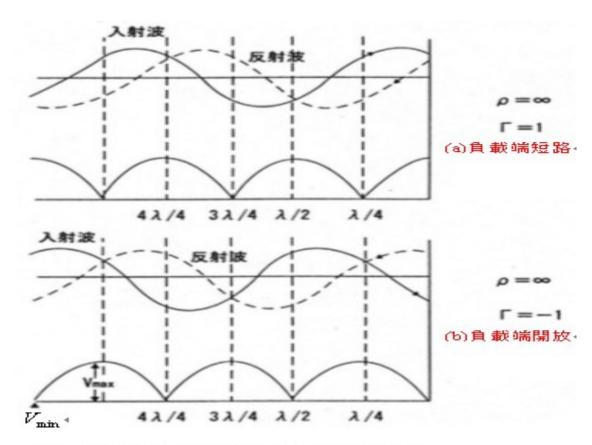

①Z<sub>R</sub>-0Ω 時(負載端短路)

$$\Gamma = -50/50 = -1 = e^{j180^{0}}$$

這意味著振幅大小相等,位相 180°相異的反射波折返信號源,如圖 1(b) 所示。

②Z<sub>R</sub>=50Ω 時(整合)

$\Gamma = (50-50) / (50+50) = 0$

這表示成為整合狀態,未發生反射波。

③Z<sub>R</sub>=1000Ω 時(不整合)

$\Gamma = (1000-50) / (1000+50) = 0.95$

④Z<sub>R-∞</sub>Ω 時(負載端開放)

$$\Gamma = (\infty - 50)/(\infty + 50) = 1 = e^{j0^0}$$

這表示振幅大小相等,位相相等的反射波折返信號源,如圖 1(a) 所示。

⑤Z<sub>R=</sub>j50Ω 時

$$\Gamma = (j50-50)/(j50+50) = 1 \angle 90^0 = j1 = e^{j90^0}$$

⑥ Γ =0.5 ∠ 45°時

$Z_{R}=50x[(1+0.5 \angle 45^{\circ})/(1-5 \angle 45^{\circ})]$

$Z_{R=}50x[(1+0.335+j.355)/(1-0.335-j0.355)]$

=69.07+j65.12( $\Omega$ )

由試算例 1 可知從負載阻抗可求得反射係數的互動關係,反過來說也可由反射係數求得負載阻抗的互動關係,不過若改用史密斯圖表方式,就可直接從圖表中輕易獲得相果。

圖1-負載端短路與負載端開放時的反射特性+

## 定常波比(VSWR)

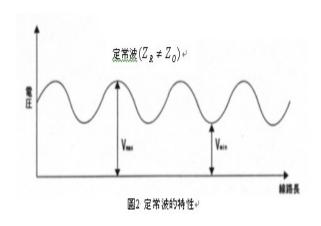

定常波比ρ與上述反射係數一樣,使用尺度表示整合狀態,定長波一旦產生反射波,就會在傳輸線路上與

入射波合成,外觀上似乎在傳輸線路上變成停止狀態的波形,波的最大值與最小值的比稱讚定在波比  $\rho$  ,亦即:

此處假設:

①整合(Z<sub>R-</sub>Z<sub>0)</sub> 時

則式(3)與(4)的反射係數 $\Gamma=0$ ,定常波比 $\rho=1$ 。

#### ②不整合時

不整合時會產生反射波,如果出現如圖 2 所示定在波時,傳輸線路便具有頻率特性。如上所述在高頻電路阻抗整合具體重要意義,如果傳輸線路的特性阻抗Z。與收信端(負載)的阻抗相同時,定常波就無法停滯,也就不會有信號傳輸問題產生,

$Z_o(\sqrt{\mathcal{L}_C})$ . 此時的線路可視為無損耗狀態,單位長度的特性阻抗 在任何位置都是一

定值,因此在形成相同傳輸線路上,任何位置的波形都與信號源波形的位相都相同,換言之從送信到收信一連串傳輸線路上的through hole(可能會形成阻抗非連續點)與信號pattern彎曲部份,必需格外謹慎考慮信號站立時間與線路長度,同時設法避免該部位發生反射現象。

# 史密斯特性圖表(Smith chart)

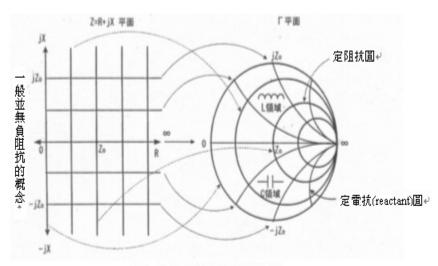

圖 3 是在直交座標上將任意點的阻抗(複素數)轉換成反射係數 平面時,阻抗平面與反射係數平面 的互動關係。由於高頻電路的 pattern 線路必需考慮分佈定數回路程傳輸線路,所以阻抗的整合也越來越重要。

處理阻抗整合概念時,在史密斯特性圖表可將線路的特性阻抗 當作基準,同時還能將它視為正規化阻抗使用。

圖3·Z平面與 F 平面的互動關係↓

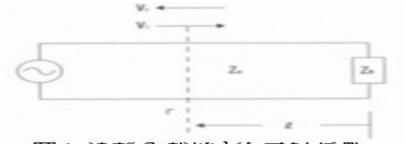

如圖 4 所示遠離負載端 $Z_R$  的反射係數 ,若以正規化阻抗z表示時,就可利用式(1)求得,亦即  $\Gamma = (Z_RZ_0-1)/(Z_R/Z_0+1)=(Z-1)/(Z+1)$

如果用z表示則變成下式:

$Z=(1+\Gamma)/(1-\Gamma)$ -----(5)

如上所述z與 是複素量,因此可轉換成下式:

$Z=r+j_X$

z平面轉換成 平面的複素數時,可將各關係代入式(5)與(6)。

$r+j_{X}=(1+\Gamma)/(1-\Gamma)$

=[1+(m+jn)]/[1+(m+jn)]

上式展開後將實數部與虛數部分開整理就變成圓的方程式,其結果如下:

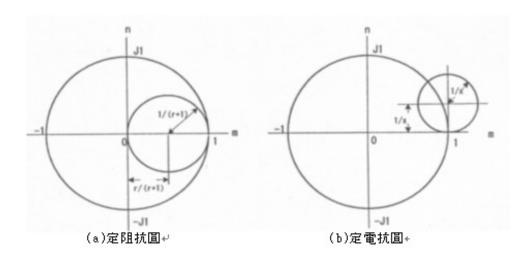

①定阻抗圓

正規化阻抗r為一定時,表示它是反射係數的圓,而圓的中心與半徑分別用下式求得:

圓的中心m=r/(r+1)

n=0

圓的半徑 1/(r+1)

例如整合時:

圓的中心 m=1/2

n=0

圓的半徑 1/2

亦即通過半徑 1 (中心的正規化阻抗z=1+j0) 時就會形成一個圓。為了獲得整合因此必需使r=1,依此前提便可利用元件L與C構成整合電路。

圖4·遠離負載端1的反射係數+

#### ②定電抗(reactant)圓

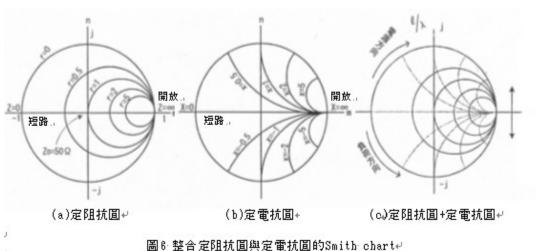

圖 5 是定阻抗圓與定電抗圓的描繪方式,圖 6 則是將定阻抗圓與定電抗圓描繪在同一平面的史密斯特性圖 表(Smith chart)。

圖5 定阻抗圓與定電抗圓的描繪方式↓

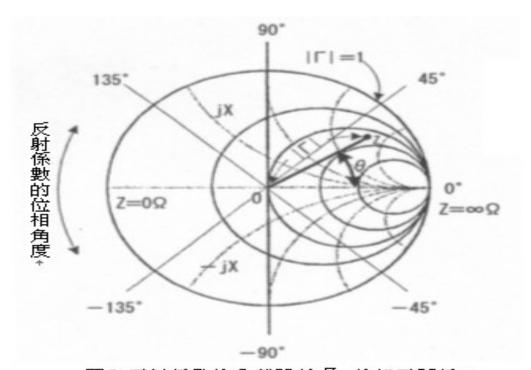

# 史密斯特性圖表的應用

使用史密斯特性圖表必需必需注意下列事項:

- ①史密斯特性圖表是在特性阻抗正規化前提下使用正規化阻抗。

- ②任意阻抗可用半徑為1的圓表示。

- ③特性阻抗正規化的正規化阻抗的 z=1 時(亦即與特性阻抗相呈整合狀),它的

- 位置相當於史密斯特性圖表平面的中心(z=1+jo)。

- ④由圖 7 可獲得負載阻抗 ZR 與反射係數  $\Gamma$  的相互關係。

- ⑤電路元件直列連接時,阻抗平面與並連都可使用 admittance。

圖7· 反射係數的負載阻抗Z。的相互關係↓

#### Immittance chart

設計交流電路時如果將阻抗與 Admittance 合併計算並將其簡易化,就可用設計傳輸線路與高頻電路時的阻抗與 Admittance 概念,使設計過程變的比較單純。圖 8 是根據上述概念用阻抗平面將 Admittance 在史密斯特性圖表上描繪的 Immittance chart,如此一來就可利用 Immittance chart 達成上述預期目標。

圖 8 Immittance chart+

若使用 Immittance chart 表示阻抗平面上某個阻抗點,衹要讀取 Admittance chart 該點的值,該值就成 為 Admittance,依此就可簡單的作阻抗轉換。不過實際上讀取阻抗平面時,如果該點是 0 點是在對稱 1800 回轉處,作業上會變得非常煩瑣,此時可利用圖 9 的轉換圖,尤其是遇到類似下列煩瑣計算,衹要利用該圖便可輕易進行阻抗轉換。

Y=1/Z

=1/(1+j1)

=[1/(1+j1)]x[(1-j1)/(1-j1)]

=0.5-j0.5

圖9 阻抗轉換圖↩

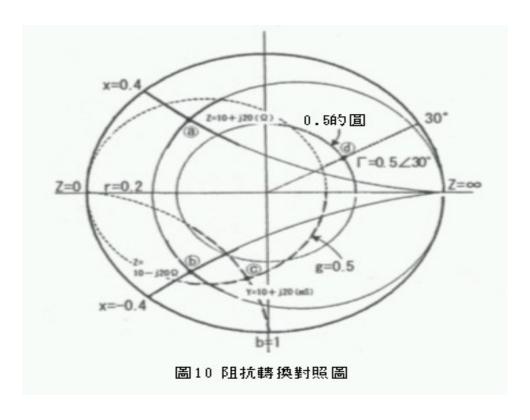

#### 【試算例2】

假設特性阻抗 為 50 Ω 時, 試將下諸值在Immittance chart描繪。

- ①  $Z=10+20 j(\Omega)$

- ② Z=10-20j(Ω)

- ③ Y=10+20 (ms)

- (4)  $\Gamma = 0.5 \angle 300$

#### ①計算正規化阻抗z

Z=(10+j20)/50

=0.2+j0.4

∴r=0.2, x=j0.4 ------參考圖 10(a)點

#### ②計算正規化阻抗z

Z=(10+j20)/50

=0.2-j0.4

## ③計算正規化Admittance

$Y = (10 + j20) xZ_0$

$=(10+j20) \times 10^{-3} \times 50$

=0.5+j1

④相對於 Immittance chart 半徑 1 的圓, 的長度等同於 0.5 的圓與 的位相角。 (參考圖 10(c)點)。

## Immittance chart的應用實例

假設阻抗Z<sub>6</sub>與電阻R、線圈L、電容C直列連接時,輸入阻抗Z<sub>6</sub>的變化可用Immittance chart檢查。類似如此的考量在獲取傳輸線路的阻抗整合,進而決定元件定數與整合電路的設計,已經成為基本的思考模式。

#### (a)阻抗(Impedance)的軌跡

為了具體說明有關輸入阻抗在阻抗平面上變化情況,因此接著以試算實例 3 作深入探討。有關直列連接元件負載的輸入阻抗,一般是將它當作阻抗平面來考慮。

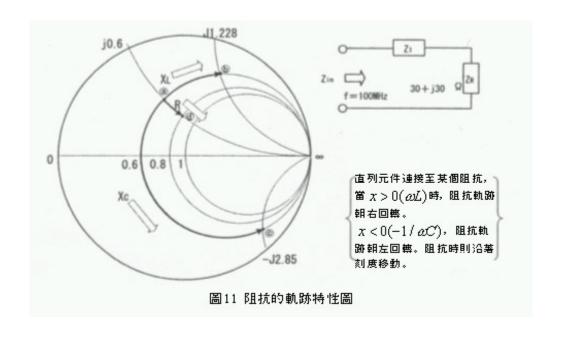

#### 【試算例3】

如圖 11 所示的電路,直列負載阻抗 $Z_k$ =30+j30(Ω)與下列元件直列連接時,試算從輸入端觀之的輸入阻抗的變化。

阻抗 R=10Ω

線圈 L=50nH

電容 C=10pF

首先計算負載阻抗ZR的正規化阻抗ZR。

$Z_R = (30 + j30/50)$

=0.6+j0.6

該正規化阻抗Z<sub>R</sub>等於圖 11 的(a)點。

①Z<sub>1</sub>=50(nH) 時, 電抗(reactance) X<sub>L</sub>的計算如下:

$X_L = jL \infty = jx2fL\Pi$

=jx2 $\prod$ x100x10<sup>6</sup>x50x10<sup>-9</sup>

=j31.4(Ω)

XL 的正規化電抗ZL計算如下:

$Z_L = j31.4/50 = j0.628$

沿著電抗的刻度右轉 0.628, 圖 11 的 (b) 點就成為正規化輸入阻抗Zin。

$Z_{in}=0.6+j1.228$

輸入阻抗Zin 的計算如下:

$Z_{in} = Z_0 x Z_{in}$

=50x(0.6+j1.228)

②Z=10(PF)時, 電抗(reactance)X。的計算如下:

$X_c = 1/jC \infty = -j(1/2fc\Pi)$

$=-i(1/2 \Pi x 100x 10^{6}x 10x 10^{-12})$

$=-j159.3(\Omega)$

X。正規化電抗Z。的計算如下: z。=-j159.3/50=-j3.186

沿著電抗的刻度左轉 3. 186, 圖 11 的(c) 點就成為正規化輸入阻抗 $Z_{in}$ = 0. 6-j2. 58

輸入阻抗 $Z_{in}$  計算如下:  $Z_{in} = 50x(0.6-j2.58)$   $= 30-j129(\Omega)$

③ $Z_1$ =10( $\Omega$ ) 時,正規化阻抗r 的計算如下: r=10/50=0.2

沿著電抗的刻度移動 0.2,圖 11 的 (d) 點就成為正規化輸入阻抗 $Z_{in}$  。 正規化輸入阻抗 $Z_{in}$  的計算如下:  $Z_{in}$ =0.8+,j0.6

輸入阻抗 $Z_{in}$ 計算如下:  $Z_{in}$ =50x(0.8-j0.6) =40+j30( $\Omega$ )

根據以上試算例3的計算結果,可歸納下列結論:

- ①阻抗L 一旦與Z。直列連接時, 就會沿著電抗的刻度向右回轉移動。

- ②電容C一旦與Z。直列連接時,就會沿著電抗的刻度向左回轉移動。

- ③阻抗R 一旦直列連接時,就會沿著電阻(resistor)的刻度移動。

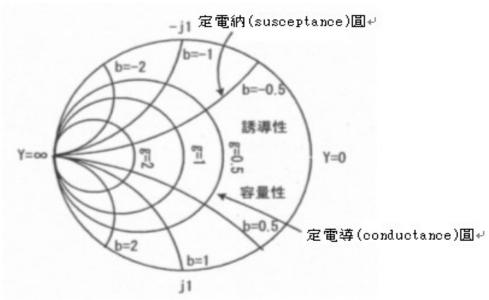

## (b) Admittance的軌跡

假設阻抗Z<sub>2</sub> 與電阻R、電阻R、線圈L、電容C並列連接時,輸入Admittance的變化可用Admittance方式考慮。此外將元件直列與負載連接時的輸入阻抗,亦可利用Admit tance方式考慮。

假設 $Z_2=30+j10(\Omega)$  與下列元件直列連接時, 試算圖 12 所示電路的Admittance。  $Z_0=50(\Omega)$ ,  $Z_0$  為傳輸線路的特性阻抗。

L=10 (nH)

C=10 (pH)

$R=10(\Omega)$

並列連接時的AdmittanceYin=Y1+Y2

$Y_2 = 1/Z_2$

=1/(30+j10)

=30-j10 (ms)

Y<sub>2</sub>的正規化Admittancey<sub>2</sub>計算方式如下:

$y_2 = (30 - j10) \times 50$

=1.5-j0.5(s)------相當於圖 12 的@點

①Z<sub>1</sub>=10 (nH) 時

$Y_{1(L)}=1/L$   $J\infty=-(1/2fL\Pi)$

$=-j(1/2 \prod x500x10^6x10^{-9})$

=-j31.85 (mS)

$Y_{1(2)}$ 的正規化 $y_{1(2)}$ 計算如下:

$$y_{WL} = -j31.85(mS) \times 50 = -j1.59(S)$$

沿著Susceptance的刻度左轉移動1.59,相當於圖12的圖點。

圖點的Admittance刻度值為正規化Admittance ying,, 由於輸入

Admittance  $Y_{in} = Y_1 + Y_2$ ,  $\boxtimes \mathcal{L} Y_{in} = Y_1 + Y_2 = Y_{1(L)} + Y_2 = 30 - j41.85 (mS)$

$\mathbb{D}$ 點的正規化Admittance  $y_{in(I)}$ 的計算如下:

$$y_{in(L)} = (30 - j41.85) \times 50$$

= 1.5 -  $j2.09(S)$

②C = 10(pF) 時

$$Y_{1(C)} = j31.4(mS) \times 50 = j1.57(S)$$

沿著Susceptance的刻度右轉移動1.57,相當於圖12的ⓒ點。

由於輸入Admittance  $Y_{in} =_{\mathfrak{U}(C)_1} + Y_2$  · 因此 $Y_{in} = Y_{\mathfrak{U}(C)} + Y_2 = 30 + j21.4 (mS)$

②點的正規化Admittance y<sub>in(C)</sub>的計算如下:

$$y_{in(C)} = (30 + j21.4) \times 50$$

= 1.5 + j1.07(S)

③  $R = 10(\Omega)$  時

$$Y_{1(R)} = 1/10 = 20(mS)$$

$Y_{\mathcal{U}(R)}$ 的正規化Admittance  $\mathcal{Y}_{\mathcal{U}(R)}$ 的計算如下:

$$y_{WR1} = 20(mS) \times 50 = 1(S)$$

沿著Conductance的刻度移動1、相當於圖12的回點。

**回點**的正規作Admittance刻度值是正規作Admittance  $y_{in(C)}$  · 計算時輸入Admittance  $Y_{1(R)}$  為  $Y_{in} = Y_{1(R)} + Y_2 = 50 - j10(mS)$  · 因此正規作Admittance  $y_{in(R)}$  的計算如下:

$$y_{in(R)} = (50 - j10) \times 50$$

= 2.5 - j0.5(S)

很拔以上試算例4的計算結果,可歸納下列結論:

- ①阻抗L一旦與 $Z_2$ 並列連接時,就會沿著Susceptance的刻度向右回轉移動。

- ②電容C一旦與 $Z_0$ 並列連接時,就會沿著Susceptance的刻度向右回轉移動。

- ③阻抗R一旦與Zo並列連接時,就會沿著Conductance的刻度移動。

#### 阻抗的整合

文接著要介紹有關設計高頻電路時的阻抗整合與史密斯特性圖表的使用方法與應用實例。

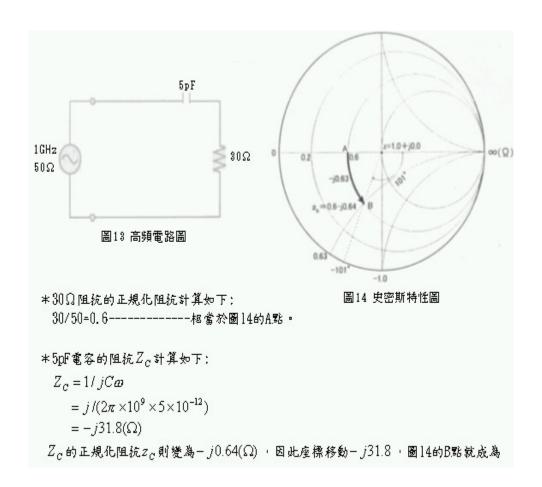

#### 【實例1】

如圖 13 所示 1GHz 高頻電路的信號源阻抗為  $50 \Omega$  時,請利用圖 14 史密斯特性圖表試算反射係數與 VSWR。

高頻電路的輸入阻抗。

\*反射係數Γ與圖14的史密斯特性圖表中半徑為1的圓呈一定比率,因此利用實測方式獲得0.44的結果,此外位相可也是從圖14的史密斯特性圖表讀取得到-101<sup>0</sup>的結果,因此反射係數Γ計算如下;

$$\Gamma = 0.44 \angle -101^{\circ}$$

\*定常波(VSWR)的計算如下:

$$VSWR = (1 + |\Gamma|)/(1 - |\Gamma|)$$

= 1.44/0.56 \(\pi 2.57\)

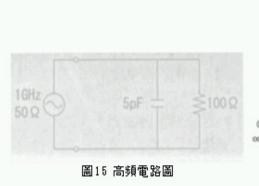

#### 【實例2】

如圖15所示1GHz高頻電路的信號源阻抗為50Ω時,請利用圖16史密斯特性圖表試算反射係數、VSWR與反射損耗(return loss)。

\*100Ω阻抗的正規化阻抗計算如下:

圖18 史密斯特性圖

\*5pF電容由於阻抗是並列連接,因此利用Admittance平面計算。 5pF電容的Admittance  $Y_C$  計算如下:

$$Y_C = jC\omega$$

=  $j2\pi \times 10^9 \times 5 \times 10^{-12}$

=  $j31.4 \times 10^{-3} (S)$

5pF電容的Admittance  $Y_c$ 計算如下:

$$Y_C = jC\omega$$

=  $j2\pi \times 10^9 \times 5 \times 10^{-12}$

=  $j31.4 \times 10^{-3} (S)$

$Y_c$ 的正規化阻抗計 $y_c$ 算如下:

$$y_c = 50 \times j31.4 \times 10^{-3} = j1.57$$

因此座標移動 j1.57 · 圖16的B點就成為高頻電路的輸入阻抗。

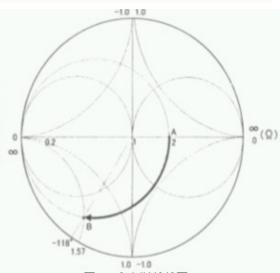

\*反射係數Γ利用實測方式獲得0.76的結果·此外位枢可也是圖16的從史密斯特性 圖表讀取得到-118<sup>0</sup>的結果·因此反射係數Γ計算如下:

$$\Gamma = 0.76 \angle - 118^{\circ}$$

\*定常波(VSWR)的計算如下:

$$VSWR = (1 + |\Gamma|)/(1 - |\Gamma|)$$

= 1.76/0.56 \(\pi\)7.29

\*反射损耗Pass是利用入射電力Pi與反射電力Pi两者的比表示,因此計算如下:

$$P_{loss} = P_r / P_i$$

$$= 10 \log |\Gamma|^2$$

$$= 20 \log 0.76$$

$$= -2.3dB$$

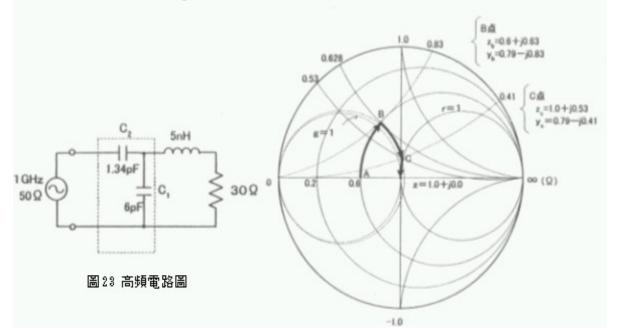

## [實例3]

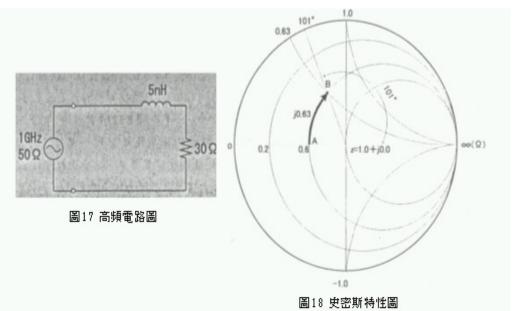

如圖17所示16Hz高頻電路的信號源阻抗為50Ω時,請利用圖18史密斯特性圖表試算反射係數與VSWR。

\*5nH電感(inductance)的阻抗 $Z_L$ 計算如下:

$$Z_{L} = jC\omega$$

$$= j2\pi \times 10^{9} \times 5 \times 10^{-12})$$

$$= -j31.4(\Omega)$$

$$\begin{split} Z_{L} &= jC\omega \\ &= j2\pi \times 10^{9} \times 5 \times 10^{-12}) \\ &= -j31.4(\Omega) \end{split}$$

$Z_L$ 的正規化阻抗 $Z_L$ 則變為j0.63( $\Omega$ ),因此座標移動-j0.63,沿著圖18的等阻抗圖移動,圖18的B點就成為高頻電路的輸入阻抗。

\*反射係數Γ與圖18的史密斯圖表中半徑為1的圓呈一定比率,因此利用實測方式獲得0.43的結果,此外位相可也是從史密斯特性圖表讀取得到-101<sup>0</sup>的結果,因此反射係數Γ計算如下;

$$\Gamma = 0.43 \angle - 101^{0}$$

\*定常波(VSWR)的計算如下:

$$VSWR = (1 + |\Gamma|)/(1 - |\Gamma|)$$

= 1.43/0.57 \Rightarrow 2.5

#### [實例4]

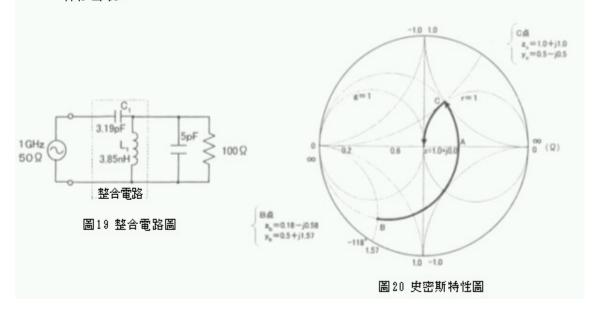

請利用「並列L+直列C」的整合電路方式,設計上述實例2的電路整合。圖20是史密斯特性圖表。

假設B點正規化阻抗為z。·正規化Admittance為y。·由史密斯特性圖表可知:

$$z_b = 0.18 - j0.58$$

$$y_b = 0.5 + j1.57$$

為取得整合因此將B點沿著電導(conductance)圓移動,求得與等阻抗圓r=1的交點,假設該點為C時,C點的正規化阻抗與 $z_c$ 正規化Admittance  $y_c$ 可由史密斯特性圖表求得:

$$z_c = 1.0 + j1.0$$

$$y_c = 0.5 - j0.5$$

此外為了能在Admittance平面上移動(虛線部份)—j2.07,因此必需將阻抗 $L_1$ 與電路並列連接,阻抗 $L_1$ 的計算方式如下所示:

$$L_1 = 50/(2.07 \times 2\pi \times 10^9)$$

$= 3.85 \text{nH}$

接著將C點沿著等阻抗圓r=1圓的中心移動,由於該移動是將阻抗平面作負方向移動,因此電容需作直列連接,電容值C<sub>1</sub>計算方式如下所示;

$$C_1 = 1/(2\pi \times 10^9 \times 50)$$

= 3.19 $pF$  ------ 整合電路如圖19所示。

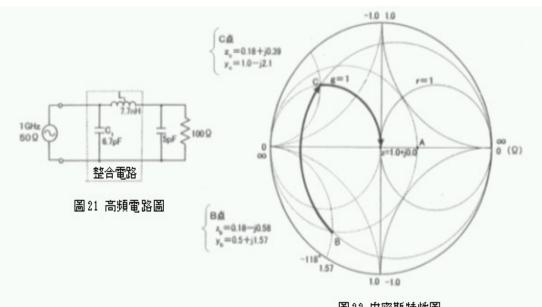

#### [實例5]

請利用「直列L+並列C」的整合電路方式,設計上述實例2的電路整合。圖22是史密斯 特性圖表。

假設B點正規化阻抗為z,與正規化Admittance為y,都與實例4個同時,由史密斯特性 圖表可知:

$$z_b = 0.18 - j0.58$$

$$y_{\lambda} = 0.5 + j1.57$$

為取得餐合因此將B點沿著等阻抗圓移動,求得與電導圓g=1的交點,假設該點為 C點滴時,C點的正規化阻抗與Z,正規化Admittance y,可由史密斯特性圖表求得:

$$z_s = 0.18 + j0.39$$

$$y_c = 1.0 - j2.1$$

由於是沿著阻抗平面上的將等阻抗圓作正方向移動·因此電感(inductance)  $L_1$  需與電路作直列連接·該移動量(虛線部份)為 j0.97·電感值  $L_1$  計算方式如下所示:

$$L_1 = (50 \times 0.97) / (2\pi \times 10^9)$$

≒ 7. 7nH

接著將 $\mathbb{C}$ 點沿著電導(conductance)圓g=1圓的中心移動,由於該移動是將Admit tance平面作正方向移動,因此電容需作並列連接,電容值 $C_1$ 計算方式如下所示:

$$C_1 = 2.1/(2\pi \times 10^9 \times 50)$$

=  $6.7 pF$  ------ 整合電路如圖 $21$ 所示。

圖22 史密斯特性圖

## 【實例6】

請利用「直列C+並列C」的整合電路方式,設計上述實例3的電路整合。圖24是史密斯 特性圖表。假設B點正規化阻抗為Z,與正規化Admittance為y,,由史密斯特性圖表可 知:

$$z_b = 0.6 + j0.63$$

$y_b = 0.79 - j0.83$

為取得餐合因此將B點沿著等電導圓移動,求得與等阻抗圓r=1的交點,假設該點為

C時·C點的正規化阻抗與Z。正規化Admittance y。可由史密斯特性圖表求得:

$$z_c = 1.0 + j0.53$$

$y_c = 0.79 - j0.41$

由於是沿著Admittance平面上作正方向移動,因此電容 $C_1$ 需與電路作直列連接, 該移動量(虛線部份)為j0.42,電容值 $C_1$ 計算方式如下所示:

$$C_1 = 0.42/(2\pi \times 10^9 \times 50)$$

$= 1.34 \text{pF}$

接著將 $\mathbb{C}$ 點沿著等阻抗圓r=1圓的中心移動,為了獲得整合因此該移動是將阻抗平面作正負方向移動-j0.53,因此電容需作並列連接,電容值 $C_2$ 計算方式如下所示

#### 圖24 史密斯特性圖

#### 【實例7】

請利用「直列C+並列L」的整合電路方式,設計上述實例3的電路整合。圖26是史密斯特性圖表。

假設B點正規化阻抗為Z,與正規化Admittance為y,都與實例6相同時,由史密斯特性 圖表可知:

$$z_b = 0.6 + j0.63$$

$y_b = 0.79 - j0.83$

為取得整合因此將B點沿著等阻抗圓移動,求得與等電導圓g=1的交點,假設該點為 C時,C點的正規化阻抗與Z。正規化Admittance y。可由史密斯特性圖表求得:

$$z_c = 0.6 - j0.49$$

$$y_c = 1.0 + j0.81$$

由於是沿著阻抗平面上作負方向移動,因此電容 $C_1$ 需與電路作直列連接,該移動量(虛線部份)為-j1.12,電容值 $C_1$ 計算方式如下所示:

$$C_1 = 1/(1.12 \times 2\pi \times 10^9 \times 50)$$

= 2.84pF

接著將 $\mathbb{C}$ 點沿著Admittance平面圓g=1圓的中心移動,為了獲得整合因此該移動是將Admittance平面作正負方向移動-j0.81,因此電威需作並列連接,電威值 $\mathcal{L}_1$ 計算方式如下所示:

(作者現任職於工研院光電所)

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(www.mweda.com),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

#### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

#### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程, 共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS, 迅速提升个人技术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

#### HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅···

课程网址: http://www.edatop.com/peixun/hfss/11.html

#### CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送3个月免费学习答疑…

#### HFSS 天线设计培训课程套装

套装包含6门视频课程和1本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

## 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了13.56MHz线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

#### 我们的课程优势:

- ※ 成立于 2004年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

#### 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

易迪拓信训 官方网址: http://www.edatop.com