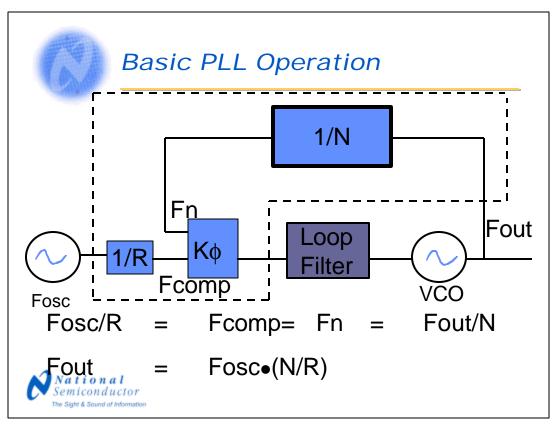

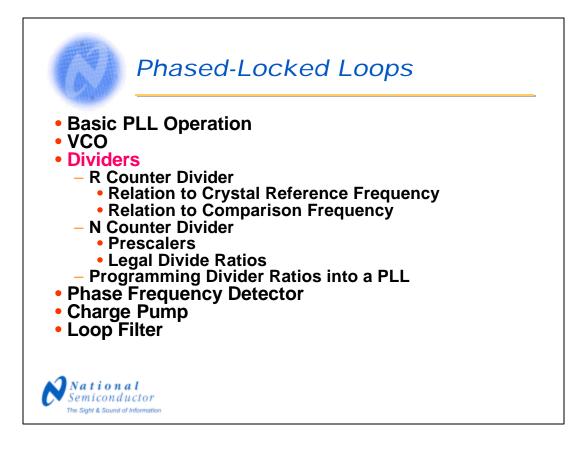

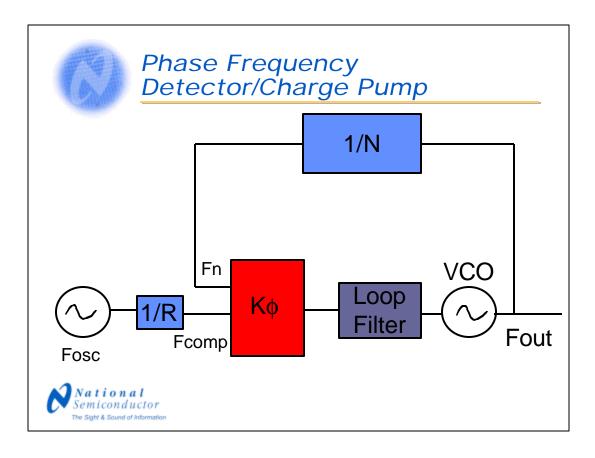

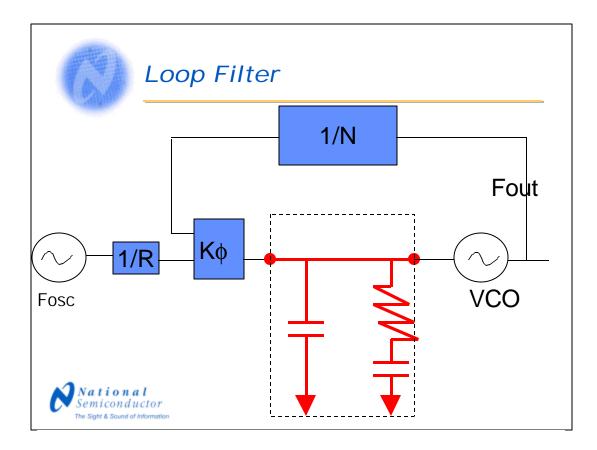

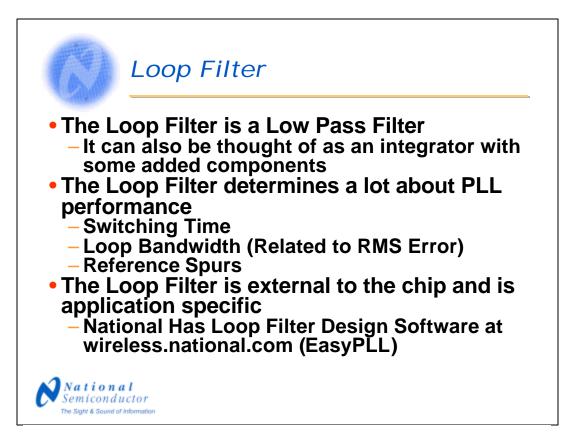

The way that the PLL works is a follows. There is a fixed crystal frequency (Fosc), which is divided down to the comparison frequency, Fcomp. Now the phase detector compares this signal to Fn. If the signals are the same, it puts out only very small corrections. If Fn>Fcomp, it sinks current. If Fn>Fcomp, it sources current. The loop filter is a low pass filter that converts these current corrections into a voltage. The VCO converts this voltage to a frequency. This output frequency, Fout is divided down by the N counter and compared to Fcomp. So the PLL basically steers the voltage to the VCO such that Fn = Fcomp.

The reason that the VCO can not be simply driven by a DAC is that VCOs have wide process variations and the output frequency can not be accurately determined by the input voltage. Typically, the crystal frequency (Fosc) is very stable, but is limited to much lower frequencies. The PLL also provides the very important advantage that the N counter can be changed by programming it to different values. This allows the PLL to be able to synthesize many different frequencies from a fixed frequency.

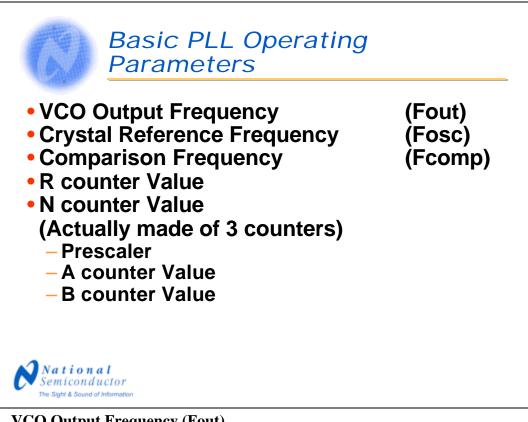

#### VCO Output Frequency (Fout)

This is the output of the whole system, which is controlled by the PLL

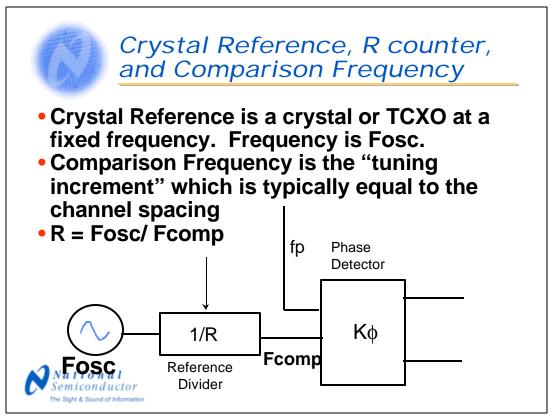

#### **Crystal Reference Frequency (Fosc)**

This is a fixed frequency. It can be provided by a TCXO (Temperature Compensated Crystal Oscillator) or a crystal. The crystal oscillator consists of a resonant circuit in the feedback path of an inverter. On some of National's PLLs, an inverter is included for using a crystal. Note that the difference between a crystal and crystal oscillator is that the crystal oscillator includes the inverter.

#### **Comparison Frequency (Fcomp)**

This can be thought of as the tuning resolution. As N is changed by 1, the output changes in increments of fcomp. For this reason, it is sometimes referred to as the channel spacing, although that name is not accurate, because there are a few isolated cases where it is something other than the channel spacing (Fractional N).

#### **R** Counter Value

This divides the fixed crystal reference frequency by R to get the comparison frequency. R is usually fixed for a given application.

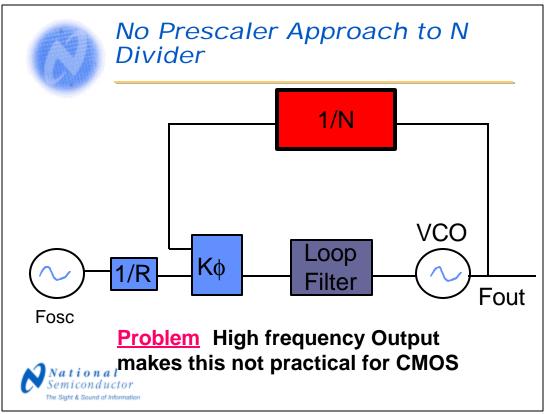

#### N Counter Value

This multiplies the comparison frequency in order to get the output frequency. Note that the output frequency is tuned by changing the N counter value. The N counter actually consists of smaller counters in order to allow high frequency operation.

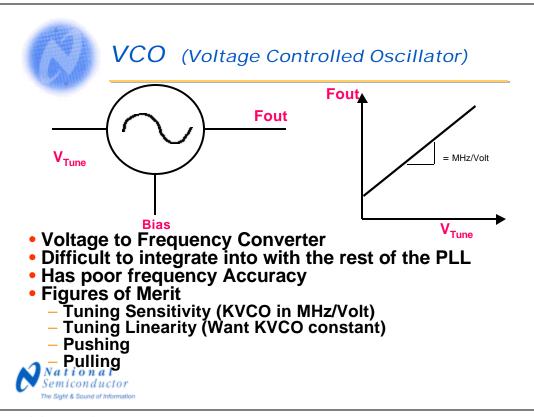

#### VCO Terminology

#### Tuning Sensitivity, Modulation Sensitivity, or KVCO

This is how much the output frequency changes for a given change in the voltage.

#### **Tuning Linearity**

Although design equations assume that the VCO gain is linear within some range, it typically has some nonlinear characteristics.

Usually, the tuning sensitivity is less at the higher tuning voltages.

#### Pulling

This is a drift in the output frequency caused by loading the VCO.

#### **Load Pushing**

A drift in the output frequency caused by changing the power supply voltage. One way to express this is in MHz/volt. It also gives an indication of how vulnerable the VCO is to power supply noise.

#### **Other comments**

The VCO contributes noise to the system. This is mostly outside the loop bandwidth.

To determine what value should be programmed into the R counter, the comparison frequency must be known first. The comparison frequency is often chosen equal to the channel spacing since when N is changed by 1, the output frequency is changed by 1\*Fcomp. Choosing the comparison frequency larger than this would cause the PLL to skip over channels, so this can not be done. The comparison frequency could be chosen smaller, but this would result in worse phase noise and a slower lock time -- the performance would not be as good. The restriction that the comparison frequency can not be chosen larger than the channel spacing applies only to integer N PLLs, not fractional N PLLs.

The crystal reference must be chosen so that is an integer multiple of the comparison frequency. Since Fcomp = Fosc / R, the value from the R counter can be easily determined.

# **N Value Calculation**

N is simply the output frequency divided by the comparison frequency.

# **Problem with Using a Simple Counter for the N Counter**

However, since the output frequency is typically high frequency, it is not practical to build it as a single counter because the high frequency process is good for the high frequency signal, but not so good for the rest of the functions on the PLL. This is why this is not used, except for low frequency.

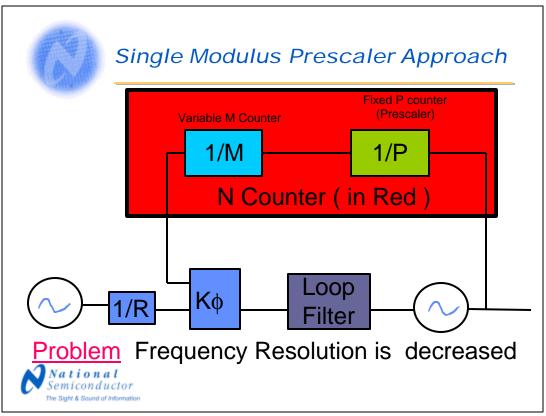

### **Single Modulus Prescaler**

This gets around the high frequency problem but sacrifices tuning resolution. This is why the Dual Modulus Prescaler (Next Slide) is typically used. It is possible to reduce the comparison frequency by a factor of P, but this results in higher noise, and higher reference spurs.

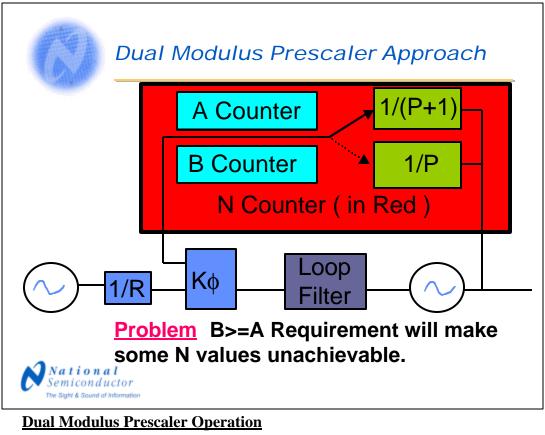

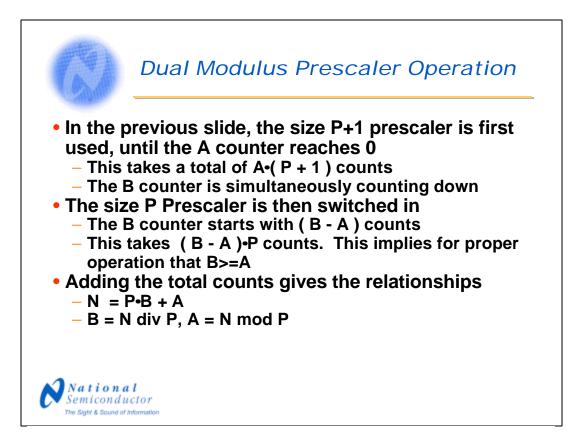

| 1.          | Initially, the size P+1 prescaler is used.                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------|

| 2.          | Every P+1 cycles of the VCO, both the A and the B counters are decreased by 1.                               |

| 3.          | This is continued until A=0. This takes a total of $A^*(P+1)$                                                |

| VCO cycles. |                                                                                                              |

| 4.          | Now the size P prescaler is switched in. Every P VCO cycles,                                                 |

|             | The B counter is decreased by 1. Since the B counter was previously counting, this takes (B-A)*P VCO cycles. |

| 5.          | When the B counter reaches 0, 1 pulse is given to the fp signal.                                             |

|             | This results in making $N=A^{*}(P+1)+(B-A)^{*}P = P^{*}B+A$ . Note                                           |

|             | also that this implies B>=A for proper operation                                                             |

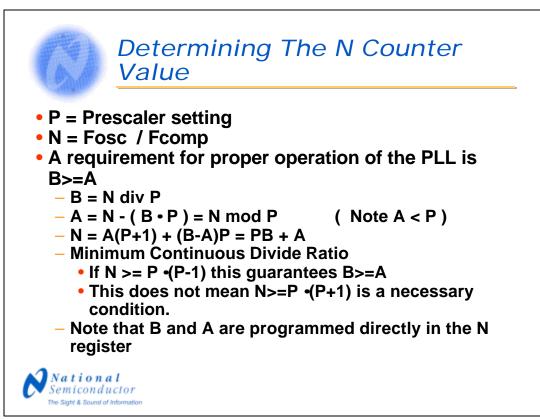

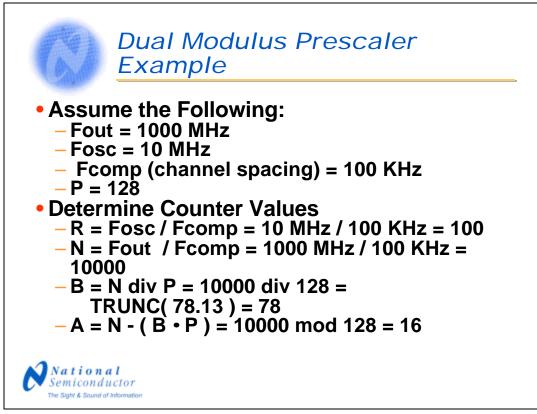

To program in a value for the N counter, the A counter, B counter, and prescalers are specified, which specifies N. Note from the proceeding slide that B>=A. This must be checked for each value of N programmed into the chip. A prescaler must be chosen before these calculations are used. e.g. for a 64/65 prescaler, P = 64

Recall:

equation 1:  $N = P^*B + A$

to determine B, apply the div operation ( also called "trunc" which means divide and disregard the remainder ) to both sides of the equation to yield:

N div P = ( P\*B + A ) div P = P\*B div P + A div P = B

(recall that A div P = 0 since A< P)

#### $\mathbf{B} = \mathbf{N} \operatorname{\mathbf{div}} \mathbf{P}$

Once B is known, A can be determined algebraically, or by applying the mod operation ( short for "modulo", which means disregard the quotient and take only the remainder)

N mod P = (P\*B+A) mod P = P\*B mod P + A mod P = A mod P A = N mod P

The minimum continuous divide ratio is a sufficient condition, but not a necessary condition. In other words, there are a few isolated cases where  $N < P^*(P-1)$ , yet the prescaler is still usable.

If  $N \ge P^*(P-1)$ , then  $B \ge P-1$ . However, since  $A \le P$ , this guarantees  $B \ge A$ . This is convenient in checking a range of N values.

Note that is is first necessary to select a prescaler to use. In this case, a 128/129 prescaler is used. If the initial selection of prescaler does not work, they try a different prescaler. The available prescalers are specified in the selection guide and the data book. After the prescaler is chosen, it is essential to confirm that  $B \ge A$  for that particular value of N for proper operation.

For this particular example, the minimum continuous divide ratio is 128\*(128-1) = 16256. Since 16256 is greater than N = 10000, we can not conclude yet that this is a legal N value, and it is necessary to check B>=A. Had N been greater than 16256, the work would have been done. Here is a summary of some of the other N values.

| <u>N</u>               | <u>B</u> | <u>A</u> | <u>Legal Divide Ratio?</u> |

|------------------------|----------|----------|----------------------------|

| 10000                  | 78       | 16       | yes                        |

| 10001                  | 78       | 17       | yes                        |

| 10062                  | 78       | 78       | yes                        |

| 10063                  | 78       | 79       | no                         |

| <br>10111<br>10112<br> | 78<br>79 | 127<br>0 | no<br>yes                  |

# Sufficient Prescaler Conditions

(If these conditions are met, then the necessary conditions will also be met. Note that this assumes an 11 bit B counter.)

| Prescaler | Min. N       | Max. N     |

|-----------|--------------|------------|

|           | (Continuous) |            |

| 8/3       | 56           | 16383      |

| 16/17     | 240          | 32767      |

| 32/33     | 992          | 65535      |

| 64/65     | 4032         | 131071     |

| 128/129   | 16256        | 262143     |

| P/(P+1)   | P•(P-1)      | 2047•P+P-1 |

-

This chart is included for reference.

The minimum N value is the minimum continuous divide ratio for the given prescaler. Note that smaller prescalers have lower minimum continuous divide ratios.

The maximum value of N is limited by the fact that the B counter has a finite number of bits. In this case, it is assumed that the B counter has 11 bits. This is true of the majority of National's PLLs.

This chart can be used to help determine which prescaler can be used. If the desired value of N is below the minimum N listed, it still may be achievable, and the only way to know is to check  $B \ge A$ . Note that this assumes an 11-Bit B counter. Some parts have a different size B counter.

Also be aware that for the lmx2350/52 only, these parts have the requirement  $B \ge A+2$ . This rule only applies to these 2 parts.

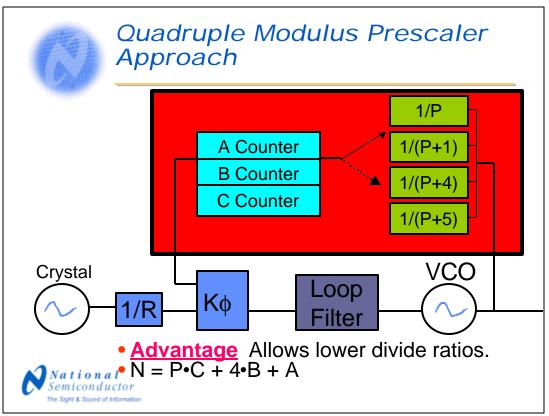

#### **Quadruple Modulus Prescaler Operation**

The quadruple modulus prescaler works by having four possible values to use as a prescaler, although only three are used for any given N value.

#### Solving for C, B, and A

A greatly simplifying assumption is that P is a multiple of 4. Practically, this turns out to be true just about all the time. Assuming this, we get:

C = N div P $A = N \mod 4$ B = (N - P\*C)/4

Note that C>=max $\{A,B\}$  for proper operation Note that A<4 and B<P/4 are restrictions for A and B as well.

The phase - frequency detector is integrated with the charge pump. On some PLLs, the outputs  $\phi r$  and  $\phi p$  are given so that an external charge pump can be used.

In the PLL, the comparison frequency is compared with the frequency obtained by dividing Fout/N, often denoted fp. If these 2 frequencies are the same, then the PLL is considered to be in lock and theoretically, the output of the charge pump should be 0 ( high impedance state ). In practice there are alternating positive and negative pulses of current with a period equal to the reference period, and these pulses are about 20-50 nS wide.

When out of lock, either positive or negative pulses are given to adjust the voltage on the loop filter, which adjusts the output frequency. For instance, when the output frequency is too low, there are positive pulses pulses of current, the width of these pulses increases with the amount that the PLL is out of lock, which increase the VCO voltage, which increase the output frequency.

Theoretically, the charge pump should sink and source the same amount of current, but in practice, there will always be some degree of mismatch. This mismatch can cause reference spurs and effect lock time, and is undesirable.

National specifies a typical and maximum mismatch in the databook. The charge pump current can also vary with the voltage on the loop filter, and over temperature.

The charge pump has 3 states:

- 1. Sink Current

- 2. Source Current

- 3. Tri-state (High Impedance)

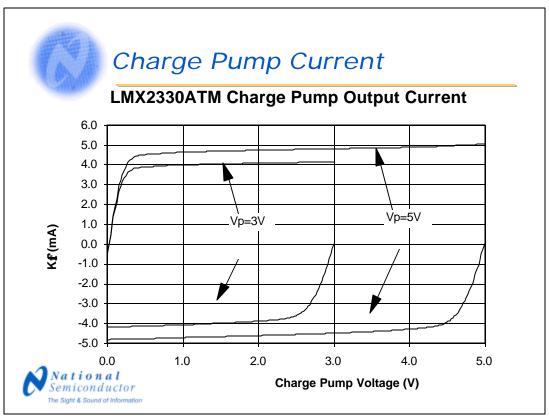

This slide shows that the amount of current sunk and sourced changes with the supply voltage and with the charge pump voltage ( which is equal to the tuning voltage to the VCO). Inferences about charge pump mismatch and variation can be made from this slide. Typically, the charge pump is not operated " Near the Rails", since the graph looks very nonlinear in this region. Note that these curves are inverted. The reason for the inversion is the way that National tests charge pump currents.

#### **Charge Pump Mismatch**

Charge pump mismatch is a measure of how well the sink and the source currents are matched. 0% mismatch is theoretically the most desirable, but sometimes a slight positive mismatch is desirable because the turn on time of the source transistor is slower than the turn on time of the sink transistor.

#### Charge Pump Balance

Balance describes how constant the charge pump currents over the charge pump voltage. A perfectly balanced charge pump would put out the exact same amount of current regardless of the charge pump voltage.

#### Charge Pump Leakage

Actually, the graph on this slide has nothing to do with charge pump leakage, although this is also an important parameter. In the locked state, the charge pump is off for most of the time. When the charge pump is off, the current should be 0 mA, but in fact there is a very slight current (usually in the nA range) when the charge pump current is off.

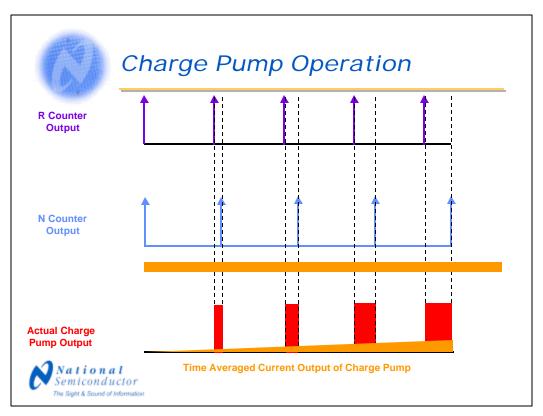

### **Charge Pump Operation**

The charge pump puts out a pulse width modulated signal. It can source current, sink current, or be high impedance. Whenever the R counter has a positive transition, there is a positive transition for the charge pump output. That means if it was sinking current, it is tri-state. If it was tri-state, it sources current. If it was already sourcing current, it continues to source current. Whenever the N divider has a positive transition, the charge pump has a negative transition. This means that if the charge pump was sourcing current, it becomes tri-state. If it was tri-state, it sinks current. If it was already sinking current, it continues to sink current.

#### **Continuous Time Approximation**

For the sake of simplicity, it is usually fair to model the charge pump current as an analog current which has a value equal to the time-averaged value. This value is shown with the orange curve. This approximation is the continuous time approximation and is valid provided that the sample rate is sufficiently high relative to the bandwidth of the loop filter. The loop bandwidth will be discussed in later sections.

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微 波、射频、天线设计研发人才的培养;我们于 2006 年整合合并微波 EDA 网(www.mweda.com),现 已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典 培训课程和 ADS、HFSS 等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子 工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、 研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电 子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

#### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电 路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材; 旨在 引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和 研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格 的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

#### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程,共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系 统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又 全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设 计方面的内容。能让您在最短的时间内学会使用 ADS,迅速提升个人技 术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

#### HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最 专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月 免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅…

课程网址: http://www.edatop.com/peixun/hfss/11.html

#### CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装,所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送 3 个月免费学习答疑…

课程网址: http://www.edatop.com/peixun/cst/24.html

#### HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线,让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

#### 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了 13.56MHz 线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

#### 我们的课程优势:

- ※ 成立于 2004 年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

#### 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

专注于微波、射频、大线设计人才的培养 **房迪拓培训** 官方网址: http://www.edatop.com

淘宝网店:http://shop36920890.taobao.cor