# THE EFFECTS OF VIAS ON PCB TRACES

# Background:

UltraCAD

Design, Inc.

Through the years we have worked with many engineers who have had strong feelings about the presence of vias on critical traces (such as fast rise time clock lines). These feelings have ranged from (a) the effects of vias are so negligible that they may be used freely, to (b) their effects are so significant that vias may not be used at all. Depending on your view, these two extremes place quite different constraints on PCB designs!

It is clear from the history of all the boards that have ever been designed in the past that vias have little impact at lower frequencies and rise times. It is only recently, as device rise times and timing issues caused by faster clock speeds have become critical PCB design issues, that the <u>concern</u> over a via's effect on PCB "transmission lines" has become a topic of discussion.

The perceived negative effects of vias may fall into one of several categories:

- 1. Vias are inherently capacitive and change the characteristic impedance of the trace.

- 2. Vias cause a step-function change in trace impedance and therefore cause reflections.

- 3. When a trace moves from one layer to another, it becomes referenced to a different reference plane, therefore

severely distorting the characteristic impedance of the trace.

- 4. A trace can move to opposite sides of an individual reference plane without significant effect, but if it moves to a layer where it is referenced to a different plane then the characteristics of the transmission line are severely distorted.

- 5. The effect of the first via is the greatest, but the effects of additional vias diminish as more vias are added to the trace.

Unfortunately, there have been few, if any, studies specifically designed to study the effects of vias while adequately controlling for other variables. This is, at least in part, due to the resources required: (a) the design of a test board, (b) its fabrication, and (c) the availability of a proper suite of test equipment and the researchers skilled in knowing how to use it.

#### Strategy:

In order to clarify some of these issues, a study was designed in order to isolate and measure individual effects that vias might have on traces. A test board was designed with 9 dual stripline traces on it, each of identical length, width, and thickness. There were four trace layers and three reference planes designed into the board. Some traces had no vias on them at all --- they were "pure" transmission lines. Others had one or more via "holes" along them, but the signal path did not go through the vias. Others passed through the via, but the signal path always referenced the same plane. Finally, others passed through the via in such a way that the stripline trace referenced a different reference plane. Each trace was terminated at each end with a high-performance RF  $50\Omega$  connector, providing access for the test equipment.

Each trace was evaluated with a time domain reflectometer, and signals were visually evaluated at both the input and output.

This study presents a model of industry cooperation for the common goal of increasing understanding. The board design and project coordination was donated by UltraCAD Design, Inc. (Bellevue, WA.) Eight boards were fabricated and donated by Dynamic Circuits, Inc. (Milpitas, CA.) The test equipment and measurement resources were provided by Professors Chi H. Chan and Yasuo Kuga at the University of Washington's Electrical Engineering Department. And the Washington Technology Center provided matching funding for equipment and resource availability. None of these partners had all the resources required to do the research on their own. Their mutual cooperation made this effort possible.

#### Procedure:

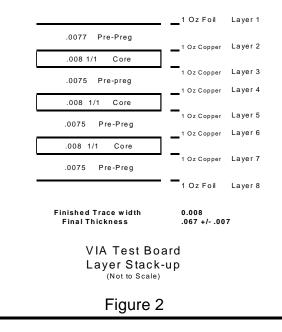

The design of the test board is shown in Figures 1 and 2. **Traces** on layers 2, 3, 6, and 7 are identical width (.008 inches), length (15 inches) and thickness (one ounce copper, approximately .0014 inch thick). They all are dual stripline traces and are as close as

possible to identical. Target characteristic impedance is  $50\Omega$ . Layers 1, 4+5, and 8 are planes (4 and 5 are electrically connected as a single plane.) The three planes are isolated from each other except for the capacitors C1 through C4. This configuration simulates a normal board with separate power and ground planes, capacitively filtered at some arbitrary spot on the board. Via holes are represented by circles along the trace. They are precisely placed along a grid that divides the trace length into eight equal increments. The vias themselves are .028 diameter plated through holes, with .050 diameter pads and .075 diameter anti-pads on the planes.

过孔大小

The number along each trace segment identifies the layer it is on. Each trace is terminated at each end by a  $50\Omega$  RF connector. The shell of the connector is connected to one of the three planes as indicated by the number adjacent to the connector.

Each trace, in turn, was connected to an HP 54120B Time Domain Reflectometer (TDR) at the left side of the board. The other end of the trace was terminated in a 50 $\Omega$  load. The TDR provides an output that can reflect the impedance at any point along the trace. Two different boards were evaluated in this manner, and the results compared. In addition, a fast rise time pulse was applied to each trace and the signal at the opposite end was recorded with a high frequency storage scope.

0 4+5 4+5 0 С 4+5 0 D 04+5 4+5 0 E 04+5 4+5 0 F 04+5 G 10 H O1 JOI  $I \otimes_1$ K G -0 10 1000 pf .1 uf 1000 pf .1 uf 4+5 0 08 80 0 4+5 4+5 0 0 1 10 0 4+5

Figure 1 Board Schematic

Trace geometries are identical. Circles represent vias along the traces. The numbers on the trace segments or connector and component pins define the layers to which they are connected.

The traces reflect increasingly "worse" cases. Traces C and G (traces A and B applied to a different analysis) are pure transmission lines. Traces D and F have vias along them, but the signal does not pass through the vias. Other traces have vias through which the signal passes to various combinations of layers, involving one or more reference planes.

#### Results:

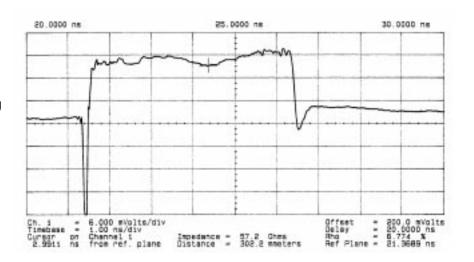

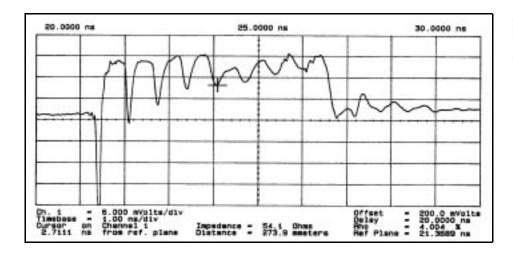

Figure 3 illustrates the TDR output for Trace C, a straight trace with no vias. It should be as close an approximation to a "pure" transmission line as can be achieved with this setup. The "round trip" time on the output is almost exactly 5 nsec. Although we do not favor using "rules of thumb", it is interesting to note that at 2 nsec per foot, the rule of thumb for pulse propagation delay along a trace, this equates exactly to the trace length of 15 inches!

The average measured impedance along the trace is about  $58\Omega$ , or about 16% over target. The variation in impedance along the trace ranges from  $57.2\Omega$  to  $59.5\Omega$ , or about 4% around the average.

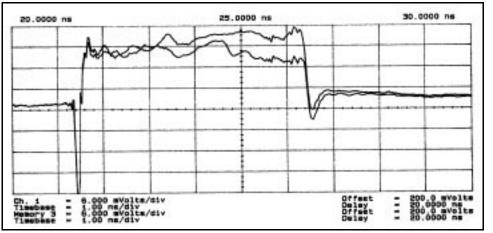

Figure 4 illustrates the TDR outputs for Trace G for both board 1 and board 2, thus comparing the repeatability between boards. This trace is also a pure transmission line, but on trace layer 2. In theory, both traces should look the same

and they should look like the trace in Figure 3. In fact, while the average impedance for each trace is about  $58\Omega$ , the range of impedance is from 57 to  $62\Omega$  for board 1 and from 56 to  $60\Omega$  for board 2.

These figures illustrate the practical problem of specifying trace impedances on PCB boards. Even under reasonably controlled conditions, impedance targets are hard to hit, and they vary by several percent from board to board, from layer to layer, from trace to trace, and even along the same trace!

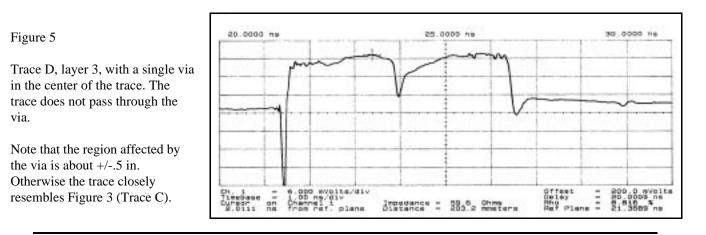

Figure 5 illustrates the TDR results for Trace D. This trace is on layer 3 with a single via in

### Figure 3

TDR output for Trace C, Layer 3

The variation in impedance along the trace is approximately 2.3  $\Omega$ or about 4%. The "round trip" trace length is about 5 nsec, implying a 15" trace at a propagation delay of 2 nsec/ft.

Figure 4

Comparative TDR outputs for Trace G, Boards 1 and 2, Layer 2.

Note the variation in impedance not only along the trace, but between the fabricated boards themselves.

the middle, but the signal does not pass through the via to another layer. Except for the via, the trace closely <u>resembles</u> Trace C (Figure 3), immediately adjacent to this trace and on the same layer. This result is typical; trace areas outside the influence of the vias exhibit very similar characteristics to adjacent traces on the same layer, but this similarity diminishes as the distance to adjacent traces increases.

The impact of the via suggests that the via is capacitive in nature, and the measured transient impedance drops about 6 or  $7\Omega$  (approximately 12%) at the lowest point.

The influence of the via is seen over about 300 Psec of trace length around the via, or almost +/-.5 inch, even though the maximum via geometry is only .075 inch. This result is consistent for all vias. This illustrates the degree that the transmission line assumptions break down in the region around the via. Although it was not studied in this effort, the region influenced by a component pin is presumably even larger.

Figure 6 illustrates what happens when more vias (7 of them) are added along the trace. Again, this trace is on layer 3 and the signal does not pass through any via. And again, the area between the vias resembles Trace C on layer 3 (with no vias) although this trace is somewhat further separated from Trace C.

The influence of the vias appears to decrease as more vias are added. We have heard engineers describe this effect as follows:

The first via has a significant capacitive effect, but this effect diminishes as more vias are added.

Figure 6, Trace F, layer 3 with multiple vias. Traces do not go through the vias.

In fact, what appears to be happening is that each via (and even the trace itself) causes a slight high frequency loss (to be described in more detail, below.) This loss in high frequency component appears to manifest itself in measurement distortion within the TDR. Thus, the TDR appears to suggest decreasing effects as more vias are added because its own measurements are being distorted by the attenuation of higher frequency harmonics. This result is typical for all traces.

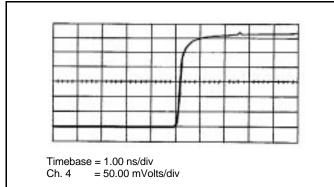

Another result tends to confirm this analysis. Figure 7 illustrates the output at the end of a typical trace as a result of a step-function input to the trace. (Figure 7 happens to illustrate Trace D.) The input voltage had a measured rise time of 40 Psec. The output signal from Trace C had a measured rise time of 231 Psec, or a slowing of the rise time by 191 Psec. This represents the

### Figure 7

Trace D, Layer 3

Output from Trace in response to a step-function input. Rise time degredation is 191 Psec.

attenuation of higher order frequency harmonics from trace losses (and perhaps connector losses) alone.

The measured rise time of Trace F (with 7 vias) was 376 Psec, suggesting the vias "cost" another 145 Psec in rise time, or about 20 Psecs per via. Other measurements along other traces were consistent with this estimate of 20 Psec reduction in rise time per via.

Interestingly enough, when the signal passed through a via to another layer, there were no additional effects that have not already been discussed. This was true even when the signal became referenced to a different plane. The effect in the immediate vicinity of the via hole was the same as if the signal did not pass through the via, and between the vias the traces took on the characteristics of layer they were on. There was some signal degradation due to the inherent nature of a transmission line and because of differences in impedance **along**  the trace. But using a via to transition to another layer of the same target impedance seemed to have no additional degradation than a did a via hole without a signal transition.

Conclusion:

In these results, a via tended to present a transient impedance discontinuity to a trace of about  $6\Omega$ . This would result in a negative reflection coefficient of about .055, or about 5%:

$$\rho = \frac{(R_L - Z_0)}{(R_L + Z_0)} = \frac{52 - 58}{52 + 58} = .055$$

Visual evaluation of various signals also suggested that reflections are small. (For example, see Figure 7.)

Vias did have a capacitive effect and tended to attenuate the very high frequency harmonics of the signal, as manifested in a slower signal rise time. But this effect, per via, was about an order of magnitude less than the losses along the trace without any vias at all (over the full 15 inches of trace). It would seem that for designs using components with rise times in the range of .5 to 1.0 nsec or slower (500 to 1000 Psecs), which is still pretty fast, a 40 Psec rise time impact as a result of a via would appear to be relatively harmless. Other Considerations:

While the results of this study were consistent across traces and boards, they do raise some other questions. For example, would vias have relatively more impact if traces were shorter? Or if via geometries were larger? Or what if we targeted a different intrinsic impedance (such as  $75\Omega$ )? We think not, but the question deserves consideration.

If a via has an impact that is seen for as much as .5 inch around the via, how do component pins (as differentiated from the components themselves) impact trace impedances in dense boards?

Although there did not seem to be any signal degradation when a signal passed through a via and became referenced to a different plane (as in the case of Trace J where the trace is alternately referenced to the top plane -- layer 1-- and the middle plane -- layers 4+5), it nevertheless seems true that the signal return path must be somewhere. And other studies have shown that for fast rise time pulses, the **return** path likes to be "close" to the signal path. If the return paths are "roaming" unpredictably around the planes, does this have an impact for EMI radiation from the board? The answer might quite likely be "yes."

Thus, the results disclosed by this study seem to be instructive, but, as always, more questions are raised.

Copyright 1994 by UltraCAD Design, Inc. May not be reproduced in any form without explicit and written approval from UltraCAD.

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微 波、射频、天线设计研发人才的培养;我们于 2006 年整合合并微波 EDA 网(www.mweda.com),现 已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典 培训课程和 ADS、HFSS 等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子 工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、 研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电 子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电 路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材; 旨在 引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和 研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格 的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

#### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程,共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系 统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又 全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设 计方面的内容。能让您在最短的时间内学会使用 ADS,迅速提升个人技 术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

# HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最 专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月 免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅…

课程网址: http://www.edatop.com/peixun/hfss/11.html

# CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装,所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送 3 个月免费学习答疑…

课程网址: http://www.edatop.com/peixun/cst/24.html

### HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线,让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

### 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了 13.56MHz 线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

#### 我们的课程优势:

- ※ 成立于 2004 年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

# 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

专注于微波、射频、大线设计人才的培养 **房迪拓培训** 官方网址: http://www.edatop.com

淘宝网店:http://shop36920890.taobao.cor