# High-Speed Backplanes Pose New Challenges to Comms Designers

As backplane speeds move beyond 3 Gbit/s, designers will encounter problems not seen at lower rates. Fortunately, through the use of modeling techniques, designers can tackle these issues head on.

The operating data rates of current state-of-the-art backplane serial links are in the 2.5- to 3.125-Gbit/s range. As silicon becomes available that can support higher data rates into the 5- and 10-Gbit/s range, comm system designers are looking for ways to support these higher rates within their existing backplanes.

In the 5- to 10-Gbit/s range, the technical challenges created by phenomenon such as reflections and crosstalk increase. In addition, new voltage- and timing-related challenges have arisen that typically do not exist in lower data rate ranges. These include skin effect, dielectric loss, inter-symbol interference (ISI), and via stub effect.

To overcome these challenges, system designers must develop accurate and efficient models for both the active and the passive components of the system. Silicon vendors also need channel models to successfully design proper on-chip circuits for implementing various techniques like equalization and reflection cancellation. By modeling the known deterministic effects of the channel, signal-integrity related problems can be understood, and techniques can be developed to minimize their impacts.

To develop a backplane model, individual models for connectors, packages, PCB traces and vias are needed. In this article, we'll examine the technical challenges that must be overcome to support 5- to 10-Gbit/s rates, and the corresponding channel model requirements.

#### **Channel Impairments**

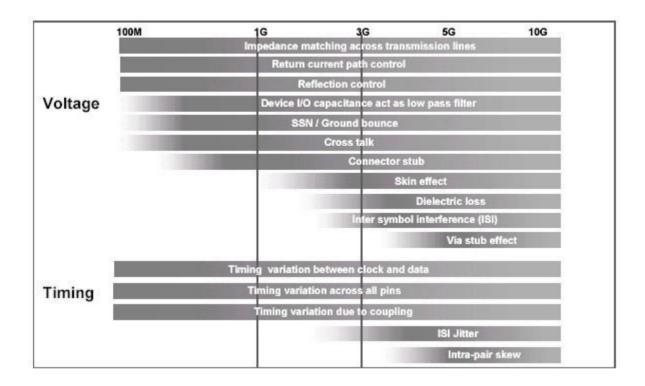

As the data transfer rate on the channel increases, "old" problems are exacerbated, and "new" problems arise that must be addressed. Figure 1 shows the key timing and voltage related impairments that must be addressed as data rates increase.

Figure 1: Above 3 Gbit/s, backplane transmission becomes a major challenge.

Figure 1 is divided into three regions of interest:

- The 100 Mbit/s to 1 Gbit/s region

- The 1 to 3 Gbit/s region

- The 3 to 10 Gbit/s region

The 100 -bit/s to 1-Git/s region is the better understood of the three. In this range the designer must compensate for the issues listed in the above drawing and remove fixed errors such as impedance mismatch and data/clock skew issues.

In the 1- to 3-Gbit/s range, the designer must make adjustments that are a function of the channel's electrical behavior, such as channel loss and distortion. These quantities are typically not known when the silicon is designed. Consequently, a feedback loop can be used to adjust the variables of concern. For example, the transmit driver output swing driving into a lossy channel can be adjusted by a feedback loop sensing the input swing at the far end receiver. The objective in this example is to overdrive the channel and compensate for its losses.

Above 3 Gbit/s, the existing variables become harder to manage, and new variables begin to emerge as shown in the above drawing. These include skin effect, dielectric loss, intersymbol interference (ISI), via stub effect, ISI jitter, and inter-pair skew. Let's look at these six in more detail starting with skin effect.

#### 1. Skin Effect

Skin effect is a physical phenomenon related to high frequency transmission on a wire. At very high frequencies, the electromagnetic field of the wire causes most of the electrical current to become crowded at the edges of the wire. This phenomenon alters the distribution of the signal current throughout the wire and changes the effective resistance on the wire. The resulting effect is increased signal attenuation at higher frequencies.

#### 2. Dielectric Loss

There are a number of PCB dielectric materials on the market today. The amount of dielectric loss in the material greatly affects signal integrity at high speeds. The lower the amount of dielectric loss, the less negative impact on the signal.

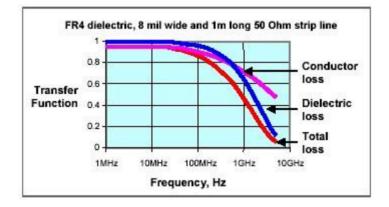

**Figure 2** shows the total loss (conductor + dielectric) on a given trace at different speeds. The signal amplitude transfer function (output divided by input signal) is normalized at 1 where there is no attenuation in the channel.

Figure 2: Loss as a function of frequency

Between 1 and 100 MHz, the amount of conductor and dielectric loss is negligible. Throughout this range, the signal transfer function remains at about 1. At 1 GHz the signal has decreased to approximately 0.5, half of its original strength. At speeds above 5 GHz the signal strength drops below 0.2, losing approximately 80% of its original strength. Thus, losses are a major issue at these high frequencies.

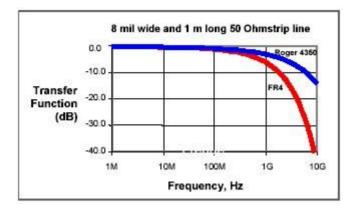

Although FR4 is the most commonly used material, it clearly does not have the best electrical characteristics when measured in terms of dielectric loss, as shown in the Figure 5. Still, FR4 is generally preferred due to its lower production costs.

Figure 3: trace loss with FR-4 and Roger dielectrics

# 3. Intersymbol Interference

ISI is a phenomenon caused by the different propagation velocities of low and high frequencies throughout a channel. The end result is a spreading of bits, also known as pulse spreading. Stated differently, transmitting a square pulse through such a channel results in a widening and flattening of the pulse at the far end. This implies that each data bit of information overlaps with its adjacent bits. This overlap can cause major distortions of the signal. At high data rates and in long channels, the ISI can be so bad that it becomes impossible to recognize an eye pattern on the oscilloscope. This is a major phenomenon limiting data transmission, and must generally be addressed starting at the 2 to 3 Gbit data rates in most system backplanes.

# 4. Via Stub Effect

At high frequencies, via stubs can cause reflections in the signal. These stubs are common on all PCBs, but at lower speeds their effects are negligible. The thicker the backplane traces, the larger the via stubs, which in turn causes the amount of signal reflections to increase. Ideally, the stub length, and resulting stub delay, should be kept as short as possible.

# 5. ISI Jitter

ISI jitter is caused by intersymbol interference. Because the pulse's energy is seen to spread into the adjacent bits with ISI, this energy will combine with the previous and next bits respectively. The adding or subtracting of energy depends on the logical value of the current pulse, and the logical values of the previous and next bits. Since the amount of energy in each bit period varies as a result, the transition time between bits also varies. A movement in time of this transition time is called jitter. Therefore, bit-dependent jitter can result. This is known as ISI jitter.

# 6. Intra-pair skew

Intra-pair skew is the amount of skew between the two signals of a differential pair. This skew can be caused by variables such as a length mismatch between traces, non-uniform bends in the signal traces, via stubs, and via transitions. Skew is normally measured as a percentage of the Unit Interval (UI). Even a slight amount of skew can dramatically impact the percentage of UI at high frequencies. For example, a 1% skew for a 30-inch trace correlates to a 5% UI mismatch at 1 Gbit/s and a 50% UI mismatch at 10 Gbit/s. This, in turn, reduces the data eye opening and increases the amount of jitter.

#### Equalization: Mitigating Impairments

Many of the channel impairments described above can be mitigated on-chip using equalization. This term is used to define circuits that can attenuate low frequencies and amplify high frequencies in either the transmit or receive directions, or both.

In one form of receive equalization, the incoming signal is sampled at different delay points. At each delay point, the signal is multiplied by a predetermined coefficient value. Each of the resulting values are then summed together to effectively recreate the signal as if it had just left the transmitter, effectively negating the effects of the various channel impairments described above.

Receive equalization is typically performed using a digital or analog adaptive filtering method. The equalization circuit examines the filtered signal output and adjusts the coefficients to optimize the signal quality through a feedback loop.

In contrast to the receive equalizer, the transmit equalizer boosts the high frequencies of a signal by a fixed amount before it is sent out. In theory, the negative effects of the previously mentioned variables will occur on the boosted portion of the signal, thereby allowing the overall signal quality at the receiver to more closely resemble that which was sent out by the transmitter. In other words, the transmitter pre-distorts the signal in the opposite way from that created in the channel so that a better quality signal can be seen at the receiver.

In both the transmit and receive path, there are two ways to set equalizer coefficients. The first is manual equalization. Also known as "set and forget", this coefficient setting technique is based on manual channel measurements. It can also be calculated on the basis of a single-bit-response (SBR) test through the channel.

The second method is to use an adaptive equalization approach. By using an adaptive algorithm such as Least Mean Square (LMS), the equalizer can optimize the signal quality by modifying the coefficients on a continuous basis. This allows the equalizer to adapt to changing conditions in the back-plane. A continuously adaptive method is far superior than the "set and forget" method because it adjusts to the changing environment automatically. This is relevant because environmental effects such as temperature and humidity changes can have a dramatic impact on the channel behavior.

#### System Modeling

Each of the points discussed above indicates an electrical variable that can impact

signal integrity over the backplane. To effectively manage the negative effects at each of these points, the physical structures impacting these electrical variables should be modeled. Once each physical structure is modeled (package, trace, via, etc.) an overall system model can be developed that is representative of the point-to-point trace from device to device.

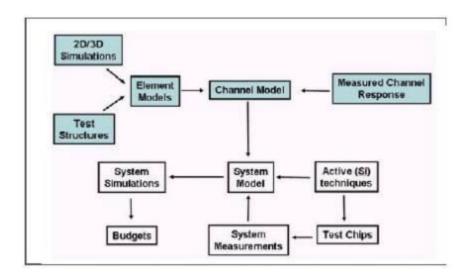

Figure 4 shows a flow chart of the modeling process.

Figure 4: System model flow chart.

The flow chart shown in Figure 4 includes test structures, 2D/3D simulations, a channel model, a system model, test chips, and system simulations. Let's look at each block in more detail.

# 1. Test Structures

The test structures include measurements that have been made at the various points in the signal path. These include package-to-board via, line card trace, line card via, backplane connector, backplane via, and backplane trace.

Physical measurements are made on the electrical characteristics of each variable. Data from these measurements are then used to construct the overall channel model.

# 2. 2D and 3D Simulations

Another way to develop component models is via 2- or 3-dimensional simulation. In this case the simulator takes the size, length, thickness, and other relevant physical parameters and calculates the relative electrical characteristics for that component. These two types of models are then used to build the channel model shown in Figure 4.

#### 3. Channel Model

The channel model includes everything except the silicon devices on each end. The channel model is built and tested and the results are compared against a measured channel response to determine whether the model is working correctly. Based on this correlation, the channel model is modified to match the results of the physical measurements. The goal is to have an accurate channel model at the frequencies of interest such that it can be used reliably as a predictor of behavior when simulating the entire system.

#### 4. System model and Active Signal Integrity Techniques

The system model includes not only the channel model, but also the silicon devices at each end. At data rates below 1 Gbit/s, the system model and the channel model should indicate in most cases that the signal degradation can be addressed using standard fixed or feedback techniques, as discussed earlier. Above 1 Gbit/s, additional signal integrity (SI) techniques must be employed to maintain overall signal quality.

Active SI, or equalization, is required if the channel model simulation output dictates that additional steps must be taken to eliminate signal degradation. This is often the case above 1 Gbit/s, and generally always required in most systems above 3 Gbit/s.

#### 4. Test chips and System Measurements

Once the active SI algorithm and circuit has been developed, test chips can be built to demonstrate that the equalization algorithms are working properly. System measurements can be taken on the test chip and on the overall system to ensure signal integrity from chip-to-chip. These results are then correlated to the system model to ensure the accuracy of the models.

#### 5. System Simulations

With a well-correlated and stable system model, the overall system simulation can be done. The system simulation takes into account other variables such as:

- Size of the channels in the chassis Number of potential cards

- Shortest distance over the backplane from card-to-card

- Longest distance over the backplane from card-to-card

Using this information, the system simulator can interpolate the electrical characteristics for all other points in the chassis. For example, if the electrical characteristics between two points are measured, with the shortest distance being two inches and the longest distance being 10 inches, the system simulator can be used to calculate the electrical characteristics for all other points in between, provided a good system model has been built.

#### Wrap Up

The backplane is a complex system containing a number of variables that can impact signal integrity. The overall number of variables to be managed and the negative impact they have on signal quality increases with speed. At speeds over 3 Gbps, not only are the negative impact of existing variables increased, but new variables such as skin effect, dielectric loss, ISI, and via stub effect, must be taken into account.

The addition of physical components within a given point-to-point link also causes signal degradation. These include PCB traces, connectors, via stubs, and the actual silicon devices themselves. Each time another impairment is factored in, signal quality is reduced at high frequencies.

To overcome these challenges, system vendors must develop accurate and well-correlated models for both the active and the passive components of the system. Silicon vendors need quality channel models to successfully design proper on-chip circuits for implementing various techniques like equalization and reflection cancellation. By modeling all the known deterministic effects of the channel, signal-integrity related problems can be well understood and minimized.

#### About the Author

Jean-Marc Patenaude is a technical marketing director in Rambus' Logic Interface Division. He holds a Bachelor of Science degree in electrical engineering from the University of Waterloo and a Master of Science degree in electronics from Carleton University. Jean-Marc can be reached at <u>imp@rambus.com</u>

中国 PCB 技术网收集及 PDF 文件制作 2004-11-03

http://www.pcbtech.net http://www.pcbbbs.com http://www.pcber.net

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微 波、射频、天线设计研发人才的培养;我们于 2006 年整合合并微波 EDA 网(www.mweda.com),现 已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典 培训课程和 ADS、HFSS 等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子 工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、 研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电 子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

#### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电 路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材; 旨在 引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和 研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格 的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

#### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程,共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系 统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又 全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设 计方面的内容。能让您在最短的时间内学会使用 ADS,迅速提升个人技 术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

# HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最 专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月 免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅…

课程网址: http://www.edatop.com/peixun/hfss/11.html

# CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装,所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送 3 个月免费学习答疑…

课程网址: http://www.edatop.com/peixun/cst/24.html

#### HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线,让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

#### 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了 13.56MHz 线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

#### 我们的课程优势:

- ※ 成立于 2004 年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

# 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

专注于微波、射频、大线设计人才的培养 **房迪拓培训** 官方网址: http://www.edatop.com

淘宝网店:http://shop36920890.taobao.cor