# Passive Circuit DesignGuide

August 2005

#### Notice

The information contained in this document is subject to change without notice.

Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Warranty

A copy of the specific warranty terms that apply to this software product is available upon request from your Agilent Technologies representative.

#### **Restricted Rights Legend**

Use, duplication or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DoD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies.

© Agilent Technologies, Inc. 1983-2005 395 Page Mill Road, Palo Alto, CA 94304 U.S.A.

#### Acknowledgments

Mentor Graphics is a trademark of Mentor Graphics Corporation in the U.S. and other countries.

$Microsoft^{\circledast}, Windows^{\circledast}, MS Windows^{\circledast}, Windows NT^{\circledast}, and MS-DOS^{\circledast}$  are U.S. registered trademarks of Microsoft Corporation.

Pentium<sup>®</sup> is a U.S. registered trademark of Intel Corporation.

PostScript<sup>®</sup> and Acrobat<sup>®</sup> are trademarks of Adobe Systems Incorporated.

UNIX<sup>®</sup> is a registered trademark of the Open Group.

Java<sup>™</sup> is a U.S. trademark of Sun Microsystems, Inc.

$System C^{\otimes}$  is a registered trademark of Open SystemC Initiative, Inc. in the United States and other countries and is used with permission.

# Contents

| 1 | Introducing the Passive Circuit DesignGuide              |      |

|---|----------------------------------------------------------|------|

|   | Getting Started                                          | 1-1  |

|   | Display Preferences                                      |      |

|   | Passive Circuit Design Flow                              |      |

|   | SmartComponents                                          |      |

|   | Automated Assistants                                     |      |

|   | Accessing the DesignGuide                                |      |

|   | The Passive Circuit DesignGuide Control Window           | 1-9  |

|   | SmartComponent Palette Access                            | 1-10 |

|   | Using the Passive Circuit DesignGuide                    | 1-11 |

|   | Čreate a New Design                                      | 1-11 |

|   | Open the DesignGuide Control Window                      | 1-11 |

|   | Auto-Design a Microstrip Line Component                  | 1-12 |

|   | Design and Analyze a Branch-Line Coupler                 | 1-13 |

|   | Optimize the Branch-Line Coupler                         | 1-14 |

|   | Display Branch-Line Coupler Analysis Results             | 1-15 |

| 2 | Using SmartComponents                                    |      |

|   | Overview                                                 | 2-1  |

|   | Placing SmartComponents                                  |      |

|   | Copying SmartComponents                                  |      |

|   | Copying Within A Design                                  |      |

|   | Copying Between Designs or Schematic Windows             |      |

|   | Editing SmartComponents                                  |      |

|   | Position and Orientation                                 |      |

|   | Parameters                                               |      |

|   | Deleting SmartComponents                                 |      |

|   | Delete From Current Design                               |      |

|   | Delete From Current Project                              |      |

|   | Delete Manually Using File System                        |      |

|   | Design, Analysis, Optimization and Layout                |      |

|   | Stand-Alone SmartComponent Usage                         |      |

|   | Using an Existing SmartComponent Within the Same Project |      |

|   | Using an Existing SmartComponent in Any Project          |      |

| 3 | Using Automated Assistants                               |      |

|   | Design Assistant                                         | 3-1  |

|   | Single Component Design                                  |      |

|   | Multiple Component Design                                |      |

|   | Simulation Assistant                                     |      |

|   | Simulation Frequency Sweep                                  | 3-2  |

|---|-------------------------------------------------------------|------|

|   | Automatically Display Results                               | 3-3  |

|   | To Simulate a SmartComponent                                | 3-3  |

|   | Using Simulation Templates                                  | 3-3  |

|   | Optimization Assistant                                      | 3-4  |

|   | To Optimize a SmartComponent                                | 3-4  |

|   | Optimization Templates                                      | 3-4  |

|   | Display Assistant                                           |      |

|   | Display Templates                                           | 3-5  |

|   | Basic Layout                                                | 3-6  |

|   | Typical Area 1 Content                                      | 3-7  |

|   | Typical Area 2 Content                                      | 3-8  |

|   | Typical Area 3 Content                                      |      |

|   | To Display SmartComponent Performance Results               | 3-9  |

|   | Layout Generation                                           |      |

|   | Creating Layout Artwork                                     | 3-10 |

|   | Updating Layout Artwork                                     | 3-10 |

| 4 | SmartComponent Reference                                    |      |

|   | SmartComponent List                                         | 4-1  |

|   | Passive Circuit DG - Lines                                  | 4-4  |

|   | MBend (Microstrip Bend Component)                           | 4-4  |

|   | MBStub (Microstrip Butterfly Radial Stub)                   | 4-5  |

|   | MCFil (Microstrip Coupled-Line Filter Element)              | 4-7  |

|   | MCLine (Microstrip Coupled Line Component)                  | 4-8  |

|   | MCorn (Microstrip Corner Component)                         | 4-9  |

|   | MCross (Microstrip Cross Component)                         | 4-10 |

|   | MCurve (Microstrip Curve Component)                         | 4-11 |

|   | MGap (Microstrip Gap Component)                             | 4-12 |

|   | MLine (Microstrip Line)                                     | 4-13 |

|   | MMndr (Microstrip Meander Line)                             | 4-14 |

|   | MRStub (Microstrip Radial Stub)                             |      |

|   | MStep (Microstrip Step Component)                           |      |

|   | MStub (Microstrip Stub)                                     | 4-19 |

|   | MTaper (Microstrip Taper Component)                         |      |

|   | MTee (Microstrip Tee Component)                             |      |

|   | Passive Circuit DG - RLC                                    |      |

|   | MICapP (Microstrip 4-port Interdigital Capacitor)           |      |

|   | MICapPG (Microstrip Grounded 2-port Interdigital Capacitor) |      |

|   | MICapS (Microstrip 2-port Interdigital Capacitor)           |      |

|   | MICapSG (Microstrip 1-port Interdigital Capacitor)          |      |

|   | MREInd (Microstrip Elevated Rectangular Inductor)           | 4-34 |

| MRInd (Microstrip Rectangular Inductor)       | 4-37  |

|-----------------------------------------------|-------|

| ······································        | 4-40  |

|                                               | 4-42  |

|                                               | 4-45  |

|                                               | 4-47  |

|                                               | 4-49  |

|                                               | 4-49  |

|                                               | 4-52  |

|                                               | 4-54  |

|                                               | 4-56  |

|                                               | 4-58  |

| $\cdot$                                       | 4-60  |

|                                               | 4-63  |

| CLFilter (Coupled-Line Filter)                | 4-63  |

|                                               | 4-66  |

|                                               | 4-69  |

|                                               | 4-72  |

| SBFilter (Stub Bandpass Filter)               | 4-75  |

| SIFilter (Stepped Impedance Lowpass Filter)   | 4-78  |

|                                               | 4-81  |

| SRFilter (Stepped Impedance Resonator Filter) | 4-84  |

|                                               | 4-87  |

| Passive Circuit DG - Matching                 | 4-90  |

| DSMatch (Double-Stub Match)                   | 4-90  |

| LEMatch (Lumped Component Match)              | 4-93  |

| QWMatch (Quarter-Wave Match)                  | 4-95  |

| RAtten (Resistive Attenuator)                 | 4-98  |

| SSMatch (Single-Stub Match)                   | 4-100 |

| TLMatch (Tapered-Line Match)                  | 4-103 |

# Chapter 1: Introducing the Passive Circuit DesignGuide

This chapter introduces the Passive Circuit DesignGuide. This manual assumes you have installed the DesignGuide with appropriate licensing codewords.

### **Getting Started**

The Passive Circuit DesignGuide provides SmartComponents and automated-assistants for the design, simulation, optimization and performance analysis of common passive microstrip structures.

The DesignGuide includes SmartComponents for microstrip structures such as lines, couplers, power dividers, filters, and matching networks. All SmartComponents can be modified when selected. Simply select a SmartComponent and redesign or verify its performance.

Automated-assistants include a Design Assistant, Simulation Assistant, Optimization Assistant, and Display Assistant, which enable you to quickly create and verify a design.

The complexity of Advanced Design System (ADS) is made easily accessible to the designer through the automated assistants. This enables a first-time or casual ADS user to begin benefiting from the capability of ADS quickly. Experienced ADS users will be able to perform tasks faster than ever before. As an example, a microstrip coupled-line filter can be designed, verified and a layout generated in a few minutes saving the designer substantial time.

#### **Display Preferences**

DesignGuides can be accessed in the Schematic window through either cascading menus or dialog boxes. You can configure your preferred method in the Main, Schematic, or Layout window. Choosing Preferences brings up a dialog box that enables you to:

**Note** Use the dialog box menu style on Windows systems because resource issues typically make the operating system unstable.

- Disable all DesignGuide menu commands except Preferences in the Main window and remove the DesignGuide menu in the Schematic and Layout windows.

- Select your preferred interface method (cascading menus vs. dialog boxes).

| l. |                                                                                                                                                         |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| I  | DesignGuide Preferences                                                                                                                                 |

|    | PLEASE NOTE: Any changes made to these options require restarting ADS to take effect.                                                                   |

|    | Show DesignGuide Menu                                                                                                                                   |

|    | The DesignGuide Preferences menu will still be available<br>in the Main window if you hide the DesignGuide menu<br>in the Schematic and Layout windows. |

|    |                                                                                                                                                         |

| l  | DesignGuide Menu Style                                                                                                                                  |

| l  | $\diamond$ Use a selection dialog box                                                                                                                   |

|    | ◆ Use cascade menus                                                                                                                                     |

|    |                                                                                                                                                         |

|    |                                                                                                                                                         |

|    | OK                                                                                                                                                      |

Close and restart the program for your preference changes to take effect.

### **Passive Circuit Design Flow**

The Passive Circuit DesignGuide follows standard design procedure:

- 1. Select a component needed for your design.

- 2. Provide specifications.

- 3. Design and analyze the component.

- 4. If the component performance needs adjustment, optimize the component.

There are two important general concepts: SmartComponents and Automated Assistants.

#### SmartComponents

The DesignGuide provides a large number of passive SmartComponents such as couplers, filters, and matching networks. SmartComponents contain specification parameters and a schematic representation of the design.

SmartComponents are manipulated using several Automated Assistants. These assistants enable you to easily design, simulate, and optimize the SmartComponents.

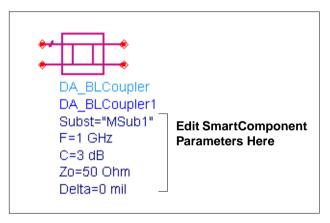

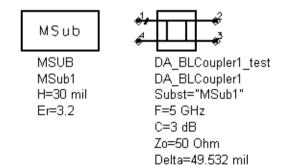

SmartComponents are smart sub-network designs that can be placed into a schematic. The Branch-Line Coupler SmartComponent is shown here.

The components are placed in the schematic by selecting the desired SmartComponent from the palette and clicking at the point where you want them placed in the schematic. The desired specifications of the SmartComponent are entered by clicking on its parameters and changing them. In addition, a dialog box containing all parameters is available by double-clicking on the SmartComponent (as shown).

| Branch-Line Coupler:1                                                                                                                | ×                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| DA_BLCoupler<br>Instance Name<br>DA_BLCoupler1<br>Select Parameter<br>Subst="MSub1"<br>F=1 GHz<br>C=3 dB<br>Zo=50 Ohm<br>Delta=0 mil | Parameter Entry Mode<br>String and Reference<br>Subst, (String)<br>MSub1<br>Edit SmartComponent<br>Parameters Here |

|                                                                                                                                      | Display parameter on schematic                                                                                     |

| Add Cut Paste                                                                                                                        | Component Options                                                                                                  |

| Subst : Substrate Instance Name                                                                                                      | e                                                                                                                  |

| OK Apply                                                                                                                             | Cancel Reset Help                                                                                                  |

The SmartComponent design schematic can be viewed by pushing into the SmartComponent's subnetwork. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. For details on the SmartComponents, refer to Chapter 4, SmartComponent Reference.

**Hint** Place a branch-line coupler SmartComponent into a schematic by clicking the *BLCplr* palette button and clicking within the Schematic window at the desired placement location. Open the parameter dialog box by double-clicking the branch-line coupler component and edit its parameters.

#### Creating a design using SmartComponents

- 1. Choose and place a SmartComponent.

- 2. Edit the SmartComponent parameters (specifications).

- 3. Design the SmartComponent using the Design Assistant.

- 4. Analyze the SmartComponent's performance using the Simulation Assistant.

- 5. Display the performance of the SmartComponent using the Display Assistant.

- 6. If necessary, optimize the SmartComponent's performance using the Optimization Assistant.

- 7. Re-analyze the SmartComponent's performance using the Simulation Assistant.

#### **Automated Assistants**

The Passive Circuit DesignGuide provides four Automated Assistants for the simplified design, simulation, optimization, and analysis of SmartComponents. Each Automated Assistant has a tab that is accessed from DesignGuide Control Window.

Design Assistant is used to generate/update a SmartComponent's schematic design. After a SmartComponent is placed and the parameters are specified, you start the Design Assistant to design the component. Subsequently, if the parameters of the SmartComponent are modified, you start the Design Assistant again to update the design. For more information, refer to "Design Assistant" on page 3-1.

Simulation Assistant is used to automatically perform a simulation of a SmartComponent. After a SmartComponent has been designed using the Design Assistant, you start the Simulation Assistant to automatically analyze the component. You can easily examine the simulation results using the Display Assistant. For more information, refer to "Simulation Assistant" on page 3-2.

Optimization Assistant is used to automatically optimize a SmartComponent design so that the desired specifications are achieved. After a SmartComponent has been analyzed using the Simulation Assistant, you can start the Optimization Assistant to automatically optimize the component. After the Optimization Assistant has finished, you can rerun the Simulation Assistant to examine the optimized performance of the SmartComponent. For more information, refer to "Optimization Assistant" on page 3-4.

Display Assistant is used to automatically display the analysis results generated using the Simulation Assistant. By starting the Display Assistant, you can quickly display the results generated from the most recent simulation of a SmartComponent. For more detailed see "Display Assistant" on page 3-5.

#### Accessing the DesignGuide

The Passive Circuit DesignGuide is accessed from a Schematic window within ADS.

1. Create or open a project.

From the ADS main window, choose File > New Project or File > Open Project, as shown here. For this example, create a new project called *QuickStart*.

| File M                                                | enu            |              |       |

|-------------------------------------------------------|----------------|--------------|-------|

| 🖥 Advanced Desig                                      | n System (I    | Main)        | _ 🗆 × |

| <u>File View Options</u>                              | <u>W</u> indow | <u>H</u> elp |       |

|                                                       | 🔁 😤            |              |       |

| File Browser                                          |                |              |       |

| B-@ adsfiles<br><b>1</b><br>⊕- <sup>●</sup> Component | htDef_prj      |              |       |

2. To open a Schematic window, choose Window > New Schematic or click the New Schematic Window toolbar button.

A new Schematic window appears, as shown here. The DesignGuide features are accessed using the menu, Control Window, and SmartComponent palettes.

To access the Passive Circuit DesignGuide features:

- 1. From the Schematic window, **DesignGuide** > **Passive Circuit**.

- 2. To access the Control Window, choose **Passive Circuit Control Window** from the *Passive Circuit* menu.

- 3. To access the documentation for the DesignGuide, choose either of the following:

- DesignGuide > Passive Circuit > Passive Circuit DesignGuide Documentation (from ADS Schematic window)

- Help > Topics and Index > DesignGuides > Passive Circuit (from any ADS program window)

| S                 | mar    | tCc   | m     | pc    | one   | ent         | P    | ale | ett | е   |   |      |      |    |     |     |   |   |    |    |   |          |     | /          | _    | Μ   | er       | าน   |   |      |      |

|-------------------|--------|-------|-------|-------|-------|-------------|------|-----|-----|-----|---|------|------|----|-----|-----|---|---|----|----|---|----------|-----|------------|------|-----|----------|------|---|------|------|

| 🛅 [ passive_prj ] | Exan   | ple   | (Sc   | her   | nati  | ic):1       | l    |     |     |     |   |      |      |    |     |     |   |   |    |    |   |          |     | 1          |      |     |          |      |   |      |      |

| File Edit Select  | View   | Inse  | ert   | Op    | otion | s 1         | Γool | s I | .ay | out | S | imul | late | 1  | Nin | dov | / |   |    |    | D | esi      | gnG | juid       | е    | He  | lр       |      |   |      |      |

|                   | 4      |       | 2     | ļ     | ↓     | <b>0+</b> 0 | ¢    | Ż   | [   | Ì   |   | 5    |      | 2  |     | +   | • | Ç | į. | €  | 5 | +2<br>C  |     | ²Q         | 8    | r ( | }        | V    |   | ₽    |      |

| Passive Circu     | iit DG | i - C | ou    | ple   | rs    |             | -    | ] [ |     |     |   |      |      |    |     |     |   | • | -  | 0  | H | <u> </u> | -   | olle<br>VA |      | đ   | <b>1</b> | REIZ |   | -90  |      |

|                   |        | •     |       |       | · ·   |             | •    | •   | +   | •   | • |      | •    | :  | :   | :   | : | : | :  | :  | • | •        | •   | :          | •    | :   | :        | :    | : | :    |      |

|                   |        | •     |       |       | · ·   |             | •    | •   | •   |     |   |      | •    |    | •   | :   | • |   |    |    | • |          |     | •          | •    | •   | •        | •    | • |      |      |

| CLCpir LCpir      |        | •     |       |       | · ·   |             | •    | •   | •   |     |   |      |      | •  | •   | :   | • | • | :  |    | • |          | •   | •          | •    | •   | •        | •    | • |      |      |

| RRCplr WDiv       |        | •     |       |       | · ·   |             |      | •   |     |     | : |      | :    | :  | :   | :   | : | ÷ | :  |    |   | :        | :   | :          | :    | :   | :        | :    | : | :    |      |

|                   |        |       |       |       | · ·   |             | •    |     |     |     |   |      | •    | •  | •   | :   | • |   | :  |    | • | •        | •   | •          | •    | •   | •        | •    | • |      |      |

|                   |        |       |       |       | · ·   |             | •    | •   | •   | :   | : | :    | :    | :  |     | •   | • | : | :  | :  |   | :        |     |            | •    | :   |          | :    | • | :    |      |

|                   |        |       |       |       | • •   |             |      |     | •   |     | • |      | •    | •  | •   | •   | • | • | •  | •  | • | •        | •   | •          | •    |     | •        |      | • | •    | •    |

|                   | Selec  | t: En | ter t | the : | start | ing (       | poin | ıt  |     |     |   | 0    | iter | ns |     |     |   |   | W  | re |   |          | 1   | .37        | 5, - | 3.3 | 75       |      |   | -0.: | 250, |

**Note** Depending on how your ADS preferences are set, a Schematic window may automatically appear when you create or open a project.

#### The Passive Circuit DesignGuide Control Window

All features are available from the Control Window including menus, a toolbar, and tab pages containing SmartComponent automated assistants.

| Menus - Toolbar - Tab Pa<br>Ressive Circuit DesignGuide                                                                   |                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| File Tools Wew                                                                                                            |                                                                                             |

| <u>  √ ♥ ♥ ₩ ₩ ₩ × </u> <u> </u>                                                                                          | <u> 2 7</u>                                                                                 |

| Current Schematic                                                                                                         | SmartComponent                                                                              |

| [ passive_prj ]: 1                                                                                                        | DA_BLCoupler1                                                                               |

| Current Design                                                                                                            | SmartComponent Capability                                                                   |

| ptest /                                                                                                                   | Design, Simulation, Optimization, Display                                                   |

| Overview Design Assistant Simulation Assistant (                                                                          | Optimization Assistant Display Assistant                                                    |

| Passive Circuit DesignGuide: SmartComponent Overvi                                                                        | ew                                                                                          |

| <ol> <li>Place a SmartComponent from one of the "Passiv<br/>(accessible from DesignGuide toolbar or menu).</li> </ol>     | ve Circuit'' palettes                                                                       |

| 2. Design SmartComponent from the "Design Assist                                                                          | ant" tab.                                                                                   |

| <ol> <li>Set SmartComponent simulation frequencies from<br/>The "Automatically Display Results" option contri-</li> </ol> | the "Simulation Assistant" tab.<br>ols automatic launching of display following simulation. |

| 4. Simulate SmartComponent from the "Simulation A                                                                         | issistant" tab.                                                                             |

| 5. If you did not choose to "Automatically Display R                                                                      | esults," open display from the "Display Assistant" tab.                                     |

| 6. If the performance is not satisfactory, optimize Sm                                                                    | nartComponent from the "Optimization Assistant" tab.                                        |

| 7. Re-simulate SmartComponent from the "Simulation                                                                        | n Assistant'' tab.                                                                          |

|                                                                                                                           |                                                                                             |

|                                                                                                                           |                                                                                             |

|                                                                                                                           |                                                                                             |

#### Passive Circuit DesignGuide Control Window

The menus and toolbar buttons perform the basic functions for each Automated Assistant (Design, Simulate, Optimize, Display) as well as display the

SmartComponent palettes. Full features are available from each of the tab pages on the window. Explore each Automated Assistant tab page by clicking on the tab at the top of each page. Explore the window menus as well to familiarize yourself with the basic DesignGuide capabilities.

The window includes the following features and functions:

- You can place the window anywhere on the screen.

- With the fields at the top of the Control Window, you can navigate multiple Schematic windows and SmartComponents.

- The *Current Schematic* drop-down list box enables you to select any of the currently opened Schematic windows. This field is also updated when *Passive Circuit Control Window* is selected from the *Passive Circuit* menu.

- The current design name is also displayed below the *Current Schematic*. The *SmartComponent* drop-down list box enables you to select any of the SmartComponents on the currently selected Schematic window.

- The *SmartComponent Capability* field informs you of what functions (design, simulate, optimize, and display) the DesignGuide can perform for that particular component.

- To close the Control Window, choose File > Exit DesignGuide from the Control Window menu bar. The window may also be closed using the window close feature of the operating system (a button marked with an 'x' at the top of the window).

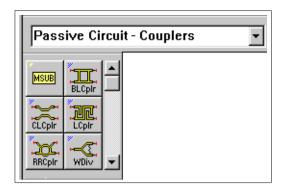

#### SmartComponent Palette Access

The SmartComponent palettes are displayed by using the Control Window menus and toolbar. (They can also be chosen from the palette list box in the Schematic window toolbar.) Six palettes are available for accessing the SmartComponents. The *Passive Circuit* palette contains all of the passive SmartComponents. The other five palettes group the components by their functionality. A blue accent in the upper-left corner of a palette button indicates the component is a SmartComponent.

### Using the Passive Circuit DesignGuide

This step-by-step example will take you through the design of a microstrip line, and the design, analysis and optimization of a branch-line coupler. After completing these examples, you should have a basic understanding of the DesignGuide.

#### **Create a New Design**

A new schematic design is needed to contain the microstrip line and branch-line coupler for the following exercises. Follow these simple steps to create a new design named Example.

- 1. Open a new Schematic window.

- 2. Choose File > New Design from the Schematic window to create a Analog/RF Network design named Example.

#### **Open the DesignGuide Control Window**

- 1. From the DesignGuide menu on the ADS Schematic window, choose **Passive Circuit**.

- 2. From the Passive Circuit window, choose Microstrip Control Window and click OK.

#### Auto-Design a Microstrip Line Component

A microstrip line can easily be designed given a substrate definition, its characteristic impedance, and length. Follow these simple steps to design a microstrip line.

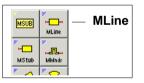

- 1. Display the Passive Circuit Lines palette. Refer to "SmartComponent Palette Access" on page 1-10.

- 2. Click the **MSUB** palette button, then click within the Schematic window at the desired placement location to place a microstrip substrate definition (MSUB) component.

- 3. Double-click the MSUB component to open the component parameter dialog box and change the substrate thickness (H) to 20 mil and the dielectric constant (Er) to 5.

- 4. In the *Passive Circuit Lines* palette, click the **MLine** palette button, then click within the Schematic window at the desired placement location to place a microstrip line.

- 5. Double-click the MLine component and change the center frequency (F) to 5  $_{GHz}$ , the characteristic impedance (Zo) to 75  $_{Ohm}$ , and the electrical length (Lelec) to 0.25 wavelengths.

- 6. Choose the **MLine** component either by clicking on it in the Schematic window or selecting it in the *SmartComponent* drop-down list box on the Control Window.

- 7. On the Control Window, click the **Design Assistant** tab, then click **Design** to generate the design for the SmartComponent.

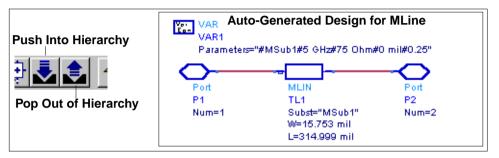

8. Choose the component MLine and click the Push Into Hierarchy toolbar button to examine the designed SmartComponent.

- 9. After examining the design, pop out of the SmartComponent by clicking the **Pop Out of Hierarchy** toolbar button.

- 10. Choose Tools > Delete SmartComponent from the DesignGuide Control Window menu to delete the Mline SmartComponent.

**Note** This is different from the *Delete* button on the ADS Schematic window toolbar.

#### Design and Analyze a Branch-Line Coupler

A branch-line coupler can be designed as easily as a microstrip line. Follow these simple steps to design and analyze a branch-line coupler.

- 1. In the *Passive Circuit Couplers* palette, click the **BLCpIr** button and then click within the Schematic window at the desired placement location.

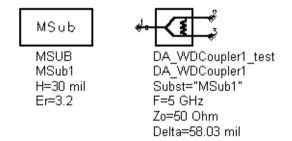

- 2. Click the BLCoupler component and change the center frequency (F) to 5 GHz.

- 3. Choose the **BLCoupler** component in the *SmartComponent* drop-down list box on the Control Window and then click the **Design Assistant** tab.

- 4. Click **Design** to generate the design for the SmartComponent.

5. Click the Simulation Assistant tab on the Control Window and enter 1 GHz start frequency, 10 GHz stop, 20 MHz step (accept default display specifications).

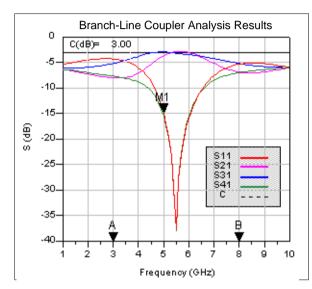

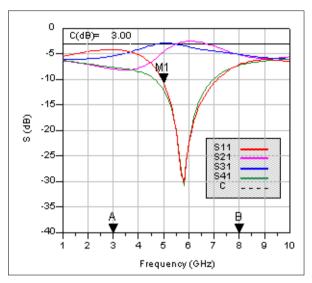

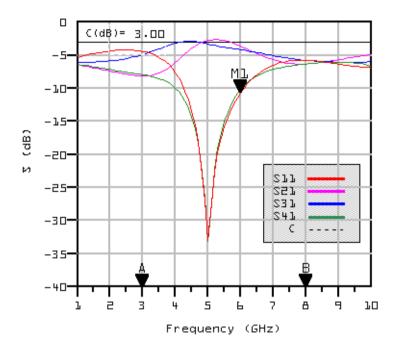

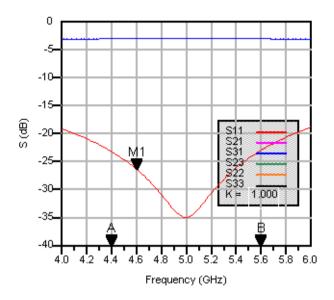

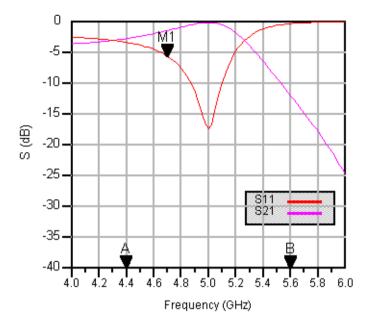

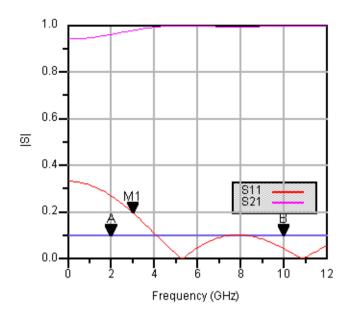

6. Click **Simulate** to analyze the SmartComponent. The analysis results are shown here.

7. Close the Display window by choosing File > Close Window from the menu.

### **Optimize the Branch-Line Coupler**

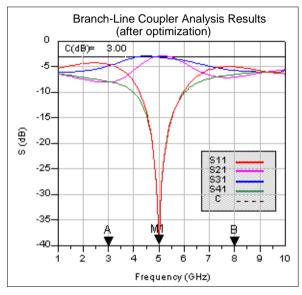

The branch-line coupler as designed in the preceding section has a center frequency of 5.5 GHz, which is different from the desired 5 GHz. The difference is due to limitations of the synthesis method used to generate the design. However, the Optimization Assistant can be used to easily optimize the design so that the center frequency is as specified.

- 1. Click the **Optimization Assistant** tab on the Control Window and click **Optimize** to optimize the SmartComponent.

- 2. Click the Simulation Assistant tab on the Control Window

- 3. Deselect the *Automatically display results* check box.

- 4. Click Simulate to re-analyze the branch-line coupler.

#### **Display Branch-Line Coupler Analysis Results**

If a SmartComponent has been analyzed with the Simulation Assistant, the analysis results can be displayed using the Display Assistant. The results from the branch-line coupler designed and analyzed above can be quickly displayed by following these simple steps.

1. Click the **Display Assistant** tab on the Control Window and click the **Display** button to display the existing simulation results.

2. Choose File > Close Window from the menu to close the Display window.

Introducing the Passive Circuit DesignGuide

# **Chapter 2: Using SmartComponents**

This chapter describes how to use SmartComponents to design your passive circuit.

### Overview

SmartComponents are *smart* sub-network designs that can be placed into a schematic and provide the container for specification parameters and a schematic representation of the design.

This DesignGuide provides a large number of passive SmartComponents such as couplers, filters, lines and matching networks. Several automated-assistants enable you to easily design, simulate (analyze), and optimize the SmartComponents.

SmartComponents can be placed, copied, edited and deleted like other components in the Advanced Design System. The basics of placement, copying, editing and deleting are described here.

The DesignGuide contains six SmartComponent palettes that provide quick and easy access to the SmartComponents. The six available component palettes are:

- All contains all of the SmartComponents.

- *Lines* contains the simple line element SmartComponents.

- *RLC* contains the distributed resistor, inductor, and capacitor SmartComponents.

- *Couplers* contains the coupler and power divider SmartComponents.

- *Filters* contains the distributed filter SmartComponents.

- *Match* contains the distributed and lumped matching SmartComponents.

There are two methods to display the desired SmartComponent palette:

Open the Passive Circuit DesignGuide Control Window by choosing DesignGuide > Passive Circuit DesignGuide > Passive DesignGuide Control Window. Display the desired SmartComponent palette by clicking one of the Component Palette buttons from the Control Window toolbar or by choosing View > Component Palette - <Palette Name> from the Control Window menu.

Choose the desired SmartComponent palette from the Component Palette drop-down list box in the Schematic window toolbar (directly above the palette).

## Placing SmartComponents

To place a SmartComponent:

- 1. Click on the desired component button in a SmartComponent palette.

- 2. Click within the Schematic window at the location you want the SmartComponent placed.

- 3. You may change the orientation of the SmartComponent before placement by choosing from the Insert > Component > Component Orientation commands or by repeatedly clicking Rotate by -90 from the schematic toolbar.

- 4. The place component mode will remain active until you choose **End Command** from the Schematic toolbar.

**Note** When a SmartComponent is initially placed, a temporary component is used to initially place and specify the parameters for the SmartComponent. This component *does not* contain a subnetwork design. After the Design Assistant has been used to design the SmartComponent, the temporary component is replaced with a permanent component. The SmartComponent is renamed to *DA\_ComponentName\_DesignName* and an autogenerated design is placed inside the SmartComponent's subnetwork design file. Subsequently, if the SmartComponent parameters are edited, the Design Assistant will need to be used again to update the subnetwork design file.

### **Copying SmartComponents**

SmartComponents can be copied within a design, to another design, or to another Schematic window.

### **Copying Within A Design**

- 1. Click the SmartComponent to be copied.

- 2. Choose Edit > Copy, then Edit > Paste from the schematic window.

- 3. Click the spot where you want the copy placed.

#### **Copying Between Designs or Schematic Windows**

- 1. Click the SmartComponent to be copied.

- 2. Choose Edit > Copy from the Schematic window.

- 3. Display the design or Schematic window you want to copy the SmartComponent to.

- 4. Choose Edit > Paste to copy the SmartComponent to the design.

- 5. Click where you want the component placed.

**Note** All copied SmartComponents will initially refer to the same SmartComponent design. When the Design Assistant is used to perform a design operation, it will transform each copied SmartComponent into a unique SmartComponent design. A design operation is accomplished by launching the Design Assistant from the DesignGuide Control Window.

### **Editing SmartComponents**

A SmartComponent's position, orientation, and parameters can be edited like any other component in ADS.

### **Position and Orientation**

A SmartComponent is moved by dragging it to any location in the Schematic window. It's orientation is changed by following these steps.

- 1. Choose Edit > Advanced Rotate/Mirror > Rotate from the Schematic window or click Rotate Items from the toolbar.

- 2. Click on the desired SmartComponent.

- 3. Rotate the component.

- 4. The rotate mode will remain active until you select the *End Command* from the toolbar.

#### Parameters

Parameters are changed by clicking on a SmartComponent parameter in the Schematic window and editing it or by double-clicking a component and editing the parameters in the component dialog box.

### **Deleting SmartComponents**

SmartComponents can be deleted from a design like other components, but completely removing a SmartComponent's files requires the actions described here.

#### **Delete From Current Design**

A SmartComponent can be deleted from a design by choosing the component and pressing the **Delete** key, clicking the **Delete** button on the toolbar, or by choosing **Edit** > **Delete** from the Schematic window. However, this does not remove the SmartComponent files from the project directory.

#### **Delete From Current Project**

To delete a SmartComponent and all associated files from your project, follow these steps.

- 1. From the DesignGuide Control Window, click the **Delete SmartComponent** button.

- 2. Click on the SmartComponent you want deleted. This will delete the SmartComponent from the current design and remove all of its files from your project.

- 3. The SmartComponent delete mode will remain active until you choose the *End Command* from the Schematic toolbar.

### **Delete Manually Using File System**

You may use your computer's file system to delete a SmartComponent by deleting the appropriate files in the network subdirectory of a project. Delete files that start with *DA\_*, *SA\_*' and *OA\_*, contain the SmartComponent title, and end with .ael or .dsn.

## Design, Analysis, Optimization and Layout

The DesignGuide contains several automated assistants that provide automatic design, analysis, and optimization for the SmartComponents. The following assistants are available.

- **Design Assistant**. The Design Assistant is used to generate and update the design contained within a SmartComponent. It invokes a synthesis engine that generates a design from the given specification. It will design and update a single SmartComponent or all SmartComponents in a design. Refer to "Design Assistant" on page 3-1 for more information.

- Simulation (Analysis) Assistant. The Simulation Assistant is used to analyze the design contained within a SmartComponent. It creates a simulation circuit containing the SmartComponent, then performs a simulation. It can also automatically display the results of the simulation. Refer to "Simulation Assistant" on page 3-2 for more information.

- **Optimization Assistant.** The Optimization Assistant is used to optimize the design contained within a SmartComponent. It creates an optimization circuit containing the SmartComponent, performs an optimization, and updates the SmartComponent. Refer to "Optimization Assistant" on page 3-4 for more information.

- **Display Assistant.** The Display Assistant is used to quickly display the performance of a SmartComponent. Display templates have been created for most of the SmartComponents. The display templates are preconfigured templates which provide a comprehensive look at the component's performance. Refer to "Display Assistant" on page 3-5 for more information.

- Automatic Layout Generation. Artwork for all of the passive circuit SmartComponents in this DesignGuide can be automatically generated. The synthesis engine used by the Design Assistant creates a schematic for the SmartComponents that is auto-layout-generation ready. The Generate Layout capability of ADS is used to generate the artwork for the SmartComponents. Refer to "Layout Generation" on page 3-9 for more information.

### Stand-Alone SmartComponent Usage

Once SmartComponents are designed and tested, they can be used as stand-alone components. The Passive Circuit DesignGuide is not needed to use them in new designs unless you wish to modify or analyze them.

### Using an Existing SmartComponent Within the Same Project

- 1. Open the Component Library window by choosinging Insert > Component > Component Library from the Schematic window or Display Component Library List from the toolbar.

- 2. Choose the project name under All > Sub-networks in the Libraries list at the left of the Component Library window. Available components will be listed in the Components list at the right of the Component Library window.

- 3. Choose the desired SmartComponent in the Components list.

- 4. Place the desired SmartComponent into your design by clicking in the Schematic window at the location you wish it placed. The insert mode will remain active until you click **End Command** on the toolbar.

### Using an Existing SmartComponent in Any Project

A library of predesigned reusable SmartComponents can be easily created. This is done by placing the reusable SmartComponents in a project. This project can be included in any project and its SmartComponents will be accessed using the Component Library. Follow these steps.

- 1. Choose File > Include/Remove Projects from the main ADS window.

- 2. Choose the project that contains the desired SmartComponent from the File Browser at the left of the *Include & Remove* window.

- 3. Click the Include button to include the project in the hierarchy.

- 4. Click OK.

- 5. Open the Component Library window by choosing Insert > Component > Component Library from the Schematic window or Display Component Library List from the toolbar.

- 6. Choose the included project name under All > Sub-networks in the Libraries list at the left of the Component Library window. Available components will be listed in the Components list at the right of the Component Library window.

- 7. Choose the desired SmartComponent in the Components list.

- 8. Place the desired SmartComponent into your design by clicking in the Schematic window at the location you wish it placed. The insert mode will remain active until you select **End Command** from the toolbar.

# **Chapter 3: Using Automated Assistants**

This chapter describes the four Automated Assistants used to design, simulate, optimize, and analyze SmartComponents, followed by instructions for creating layout artwork from the DesignGuide.

### **Design Assistant**

The Design Assistant is used to generate and update the design contained within a SmartComponent from the given specifications. It will design and update a single SmartComponent or all SmartComponents in a design.

The Design Assistant is accessed using the Passive Circuit DesignGuide Control Window. From the Control Window, full design control is enabled from the Design Assistant tab. Single component design operations can also be accomplished using the Control Window menu and toolbar.

#### **Single Component Design**

To design a single SmartComponent using the Control Window, select the desired SmartComponent either from the SmartComponent drop-down list box in the upper right corner of the Control Window or by clicking on the component in the Schematic window. The design is accomplished using one of the following methods.

- Click the **Design** button on the Design Assistant tab. The design progress is indicated on the tab page.

- Click the **Design** button on the Control Window toolbar.

- Choose Tools > Auto-Design from the Control Window menu.

#### **Multiple Component Design**

Clicking the **Design All** button on the Design Assistant tab designs all SmartComponents on the current Schematic.

**Note** To avoid screen flicker associated with the design, the Schematic window will disappear during the process.

Design progress is indicated on the tab page.

### **Simulation Assistant**

The Simulation Assistant is used to analyze the design contained within a SmartComponent. It creates a simulation circuit around the SmartComponent, then performs a simulation. If desired it will automatically display the simulation results.

The Simulation Assistant is accessed using the Passive Circuit DesignGuide Control Window. From the Control Window, full simulation control is enabled from the Simulation Assistant tab. Basic simulation can also be accomplished using the Control Window menu and toolbar.

For all simulation operations, the selected SmartComponent is designed if necessary, a simulation schematic is created, the simulation is performed, and the results are displayed. The simulation frequency sweep must be specified on the Simulation Assistant tab in the Control window.

**Note** When the Simulation Assistant is used, the simulation schematic is deleted automatically. To retain the schematic that is created, instead of the Simulation Assistant, use the Create Template option described in "Using Simulation Templates" on page 3-3.

#### **Simulation Frequency Sweep**

The simulation frequency sweep is specified on the Passive Circuit DesignGuide Control Window. If you are performing the simulation from the Control Window, click the Simulation Assistant tab and specify the sweep by entering the start frequency, stop frequency, and either frequency step size or number of points. The values entered are stored in the selected SmartComponent (as displayed in the SmartComponent drop-down list box) and will be recalled each time this SmartComponent is selected.

**Note** If a SmartComponent has been selected from the SmartComponent drop-down list box on the Control Window, default frequencies will be set for the component.

#### **Automatically Display Results**

If the Automatically Display Results box on the Control Window's Simulation Assistant tab is selected, the simulation results will be automatically displayed upon completion of the analysis.

#### To Simulate a SmartComponent

To simulate a SmartComponent using the Control Window, select the desired SmartComponent either from the SmartComponent drop-down list box in the upper right corner of the Control Window or by clicking on the component on the schematic window.

The simulation frequency sweep display option must be specified on the Simulation Assistant tab as previously described.

The simulation is then accomplished using one of the following methods:

- Click Simulate on the Simulation Assistant tab.

- Click Simulate on the Control Window toolbar.

- Choose Tools > Auto-Simulate from the Control Window menu.

### **Using Simulation Templates**

In some cases, such as when you would like to retain the schematic that is created, it is useful to simulate the SmartComponent manually.

To generate a simulation schematic around the selected SmartComponent, click the **Create Template** button on the Control Window Simulation Assistant tab.

You can examine or modify the simulation schematic, then manually start the simulation by choosing **Simulate** > **Simulate** from the Schematic window.

When you are finished, clicking the **Update from Template** button on the Simulation Assistant tab will transfer any changes you have made to the SmartComponent on the Simulation schematic to the original SmartComponent and redesign if necessary.

You can also manually close the simulation schematic by choosing File > Close Design from the Schematic window menu, although this will result is loss of any changes you have made to the SmartComponent.

## **Optimization Assistant**

The Optimization Assistant is used to optimize the design contained within a SmartComponent. It creates a optimization circuit containing the SmartComponent, then performs an optimization.

The assistant is accessed using the Passive Circuit DesignGuide Control Window. From the Control Window, full optimization control is enabled from the Optimization Assistant tab. Basic optimization can also be accomplished using the Control Window menu and toolbar.

The Optimization Assistant contains fields that indicate the objective of the optimization operation as well as the physical parameters to be altered during the process.

For all optimization operations, the selected SmartComponent is designed (if necessary), an optimization schematic is created, and the optimization is performed. The optimization results are transferred to the original SmartComponent, and this altered component is redesigned.

For each component, the optimization alters one or more of the physical design dimensions in order to make the component response more closely meet the specified performance.

### To Optimize a SmartComponent

To optimize a SmartComponent using the Control Window, follow these steps.

- 1. Select the desired SmartComponent either from the SmartComponent drop-down list box in the upper right corner of the Control Window or by clicking on the component on the schematic window.

- 2. Optimize the component by either:

- Pushing the Optimize button on the Optimization Assistant tab

- Pushing the Optimize button on the Control Window toolbar

- Selecting Tools > Auto-Optimize from the Control Window menu

### **Optimization Templates**

In some cases it may be useful to manually optimize the SmartComponent.

To generate an optimization schematic around the selected SmartComponent, press the **Create Template** button on the Control Window Optimization Assistant tab.

You can examine or modify the optimization schematic, then manually start the optimization by selecting **Simulate** > **Simulate** from the Schematic window.

When you are finished, selecting **Simulate** > **Update Optimization Values** will cause the optimized values to appear in the *VAR* element in the schematic lower left corner for your inspection.

Pressing the **Update from Template** button on the Optimization Assistant tab will transfer the optimization results to the original SmartComponent and redesign.

You may also manually close the optimization schematic using File > Close Design from the Schematic window menu, although this will cause optimization results to be lost.

## **Display Assistant**

The Display Assistant is used to easily and quickly display the performance of a SmartComponent.

The Display Assistant is accessed using either the Passive Circuit DesignGuide Control Window. From the Control Window, full display control is enabled from the Display Assistant tab. Basic display selection can also be accomplished using the Control Window menu and toolbar.

### **Display Templates**

The display templates are preconfigured templates that provide a comprehensive look at the performance of the component. Display templates have been created for most of the SmartComponents. This includes all of the RLC, coupler, filter and matching components. The line components do not have auto-simulation, auto-optimization or auto-display capability because of their simplicity.

You can create your own displays or modify the included display templates using the built in features of Advanced Design System, but in most situations, the included display templates will provide all the information you need.

The display templates opened by the Display Assistant have common features that are discussed here. For features unique to the display templates of some SmartComponents, refer to Chapter 4, SmartComponent Reference.

In some cases it may be useful to use one of the display templates provided with the DesignGuide for other applications.

To gain access to one of these templates, select the desired template from the Available Templates field and press the **Open Display Template** button on the Control Window Display Assistant tab.

You can then insert a dataset of your choice using the dataset pull-down list box in the upper left corner of the display. You may find that some parameters in the display template are not defined in the selected dataset and may want to make appropriate modifications to the display. These changes can be saved using the commands in the display File menu.

#### **Basic Layout**

Following is the basic layout of the display templates.

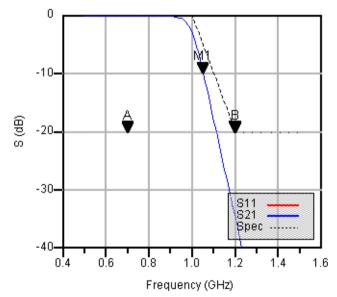

Area 1 of the display template contains a graph of the most important parameters of the SmartComponent.

Area 2 contains several graphs that give a comprehensive look at the component's performance.

Area 3 contains a table listing the basic specifications and performance of the component.

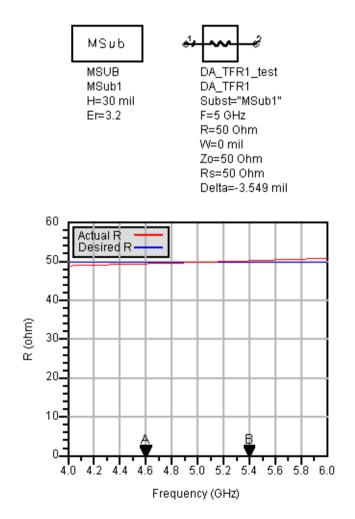

#### **Typical Area 1 Content**

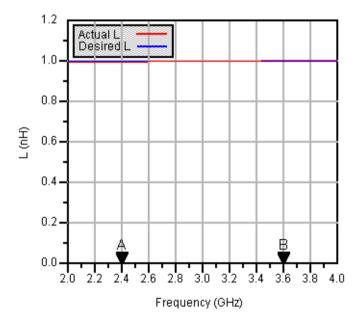

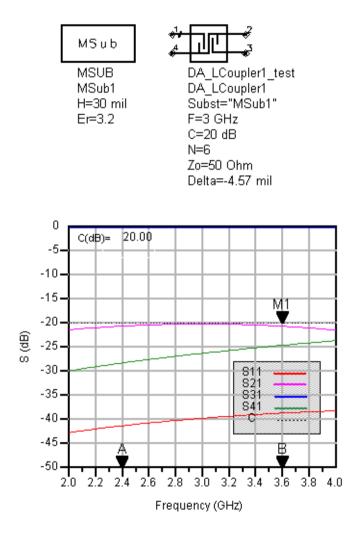

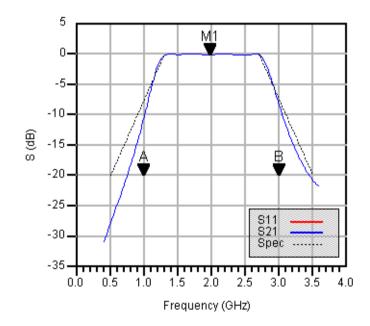

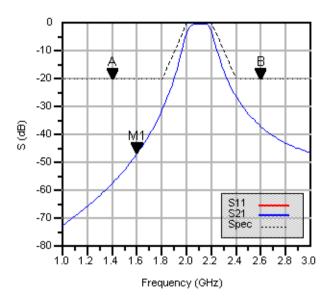

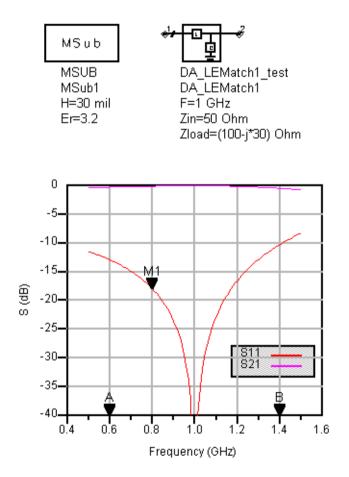

This is a typical Area 1 graph. The frequency range of the graph is determined by the Simulation Assistant. As you change the frequency range in the Simulation Assistant, this graph will update appropriately.

The markers A and B are used to define the frequency range of the graphs in Area 2. This feature is used to zero in on the region of interest and obtain a comprehensive look at the component's performance.

The marker M1 can be moved by dragging it with the mouse. The performance at the frequency given by M1 will be shown in the table in Area 3.

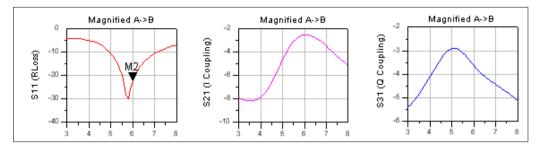

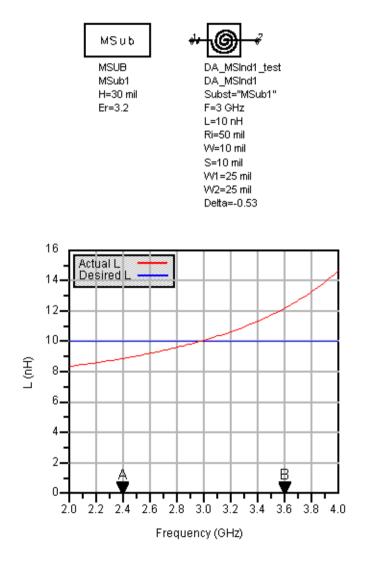

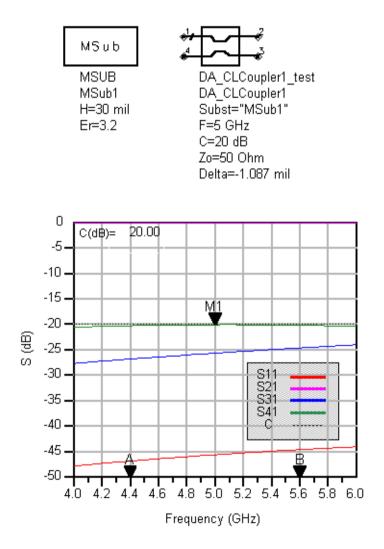

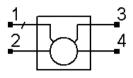

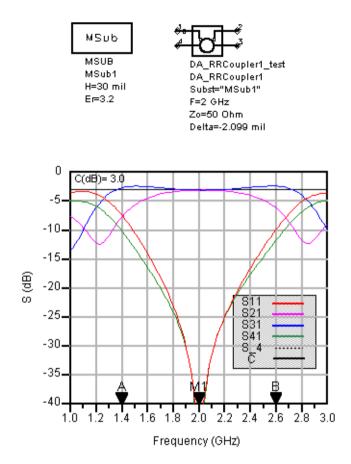

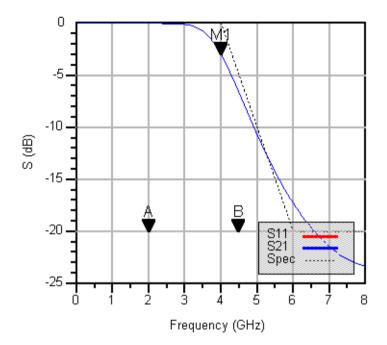

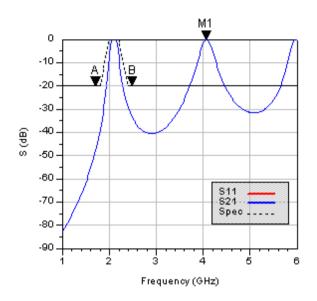

### **Typical Area 2 Content**

Typical graphs from Area 2 are shown here. These graphs provide a quick, comprehensive look at the component's performance. Their frequency range is determined by the location of the "A" and "B" markers found in the main graph.

Any markers such as M2 shown here can be moved by dragging them with the mouse. Performance criteria at the marker frequency will be displayed in the table in Area 3.

|                                                                                                                                                                  | F    | S11                                                         | S21                        | S31                         | S41      | PhaseD |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------|----------------------------|-----------------------------|----------|--------|

| Desired Center Frequency                                                                                                                                         | 5.00 | -10.72                                                      | -4.64                      | -2.91                       | -12.15   | 84.94  |

| Actual Center Frequency                                                                                                                                          | 5.80 | -30.15                                                      | -2.64                      | -3.42                       | -30.81   | 90.23  |

| Change/Worst A->B                                                                                                                                                | 5.00 | -4.20                                                       | -8.16                      | -5.41                       | -7.22    | 70.77  |

| Marker M1                                                                                                                                                        | 5.00 | -10.72                                                      | -4.64                      | -2.91                       | -12.15   | 84.94  |

| Marker M2                                                                                                                                                        | 6.00 | -22.47                                                      | -2.54                      | -3.65                       | -22.25   | 89.63  |

| F: Frequency (GHz)<br>1: Input Port<br>2: In-phase (I) Port<br>3: Quadrature (Q) Port<br>4: Isolated Port<br>C: Desired Coupling<br>PhaseD: I-Q Phase Difference |      | Note: Chang<br>over the ran;<br>of F and Pha<br>S-parameter | ge from ma<br>IseD are giv | rker A to B.<br>/en, and th | The char | ige    |

#### **Typical Area 3 Content**

A typical table from Area 3 is shown here. The white rows show the desired specifications and important performance criteria for the component. The gray rows give the performance criteria at the user defined marker frequencies. The box below the table provides explanatory information for the table.

## To Display SmartComponent Performance Results

Before using the Display Assistant, a valid dataset from a simulation of the selected SmartComponent must exist in the current project data directory. This simulation can be conveniently accomplished using the Simulation Assistant. Refer to "Simulation Assistant" on page 3-2 for details on this step.

To display results from a SmartComponent simulation using the Control Window, select the desired SmartComponent either from the SmartComponent drop-down list box in the upper right corner of the Control Window or by clicking on the component on the schematic window. The display is then launched using one of the following methods.

- Push the Display button on the Display Assistant tab.

- Push the **Display** button on the Control Window toolbar.

- Select Tools > Auto-Display from the Control Window menu.

If no valid dataset exists for the selected SmartComponent, the **Display** button on the Display Assistant tab will be insensitive. If the toolbar or menu are used to try to display the results, a message will appear indicating that no dataset exists.

## Layout Generation

The Design Assistant creates a schematic for the SmartComponents that is ready for auto-layout generation. Artwork for all of the Passive Circuit DesignGuide SmartComponents can be automatically generated. The ADS Generate Layout capability is used to generate the artwork for the SmartComponents.

Note You need an Advanced Design System Layout license to use this feature.

## **Creating Layout Artwork**

To create artwork for SmartComponents, follow these steps:

- 1. Choose and place the desired SmartComponents in the schematic window.

- 2. Specify the desired parameters for each SmartComponent.

- 3. Design the SmartComponents using the Design Assistant.

- 4. Select Layout > Generate/Update Layout from the Schematic window.

- 5. Choose **OK** in the Generate/Update Layout box.

The artwork for each SmartComponent and any other components that have associated artwork will be displayed in the Layout window. If the status report checkbox is selected in the Generate/Update Layout box, a layout generation status report will also be opened.

## **Updating Layout Artwork**

To edit the properties of a SmartComponent and update the associated artwork, follow these steps:

- 1. Choose the desired SmartComponent in the schematic window.

- 2. Edit the desired parameters of the SmartComponent.

- 3. Design the SmartComponent using the Design Assistant.

- 4. Select Layout > Generate/Update Layout from the Schematic window.

- 5. Select **OK** in the Generate/Update Layout box.

The artwork for the SmartComponent will be updated and displayed in the layout window.

# **Chapter 4: SmartComponent Reference**

This chapter provides detailed information for all passive circuit SmartComponents.

## SmartComponent List

**Note** A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

#### **Passive Circuit DG - Lines**

MBend (Microstrip Bend Component) MBStub (Microstrip Butterfly Radial Stub) MCFil (Microstrip Coupled-Line Filter Element) MCLine (Microstrip Coupled Line Component) MCorn (Microstrip Corner Component) MCross (Microstrip Cross Component) MCurve (Microstrip Curve Component) MGap (Microstrip Gap Component) MLine (Microstrip Line) MMndr (Microstrip Meander Line) MRStub (Microstrip Radial Stub) MStep (Microstrip Step Component) MStub (Microstrip Stub) MTaper (Microstrip Taper Component)

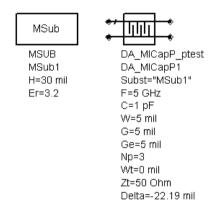

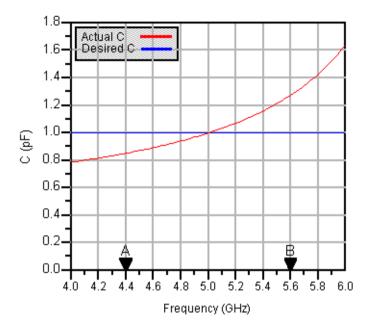

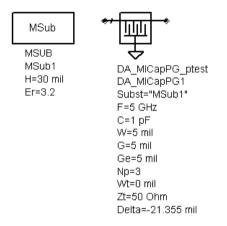

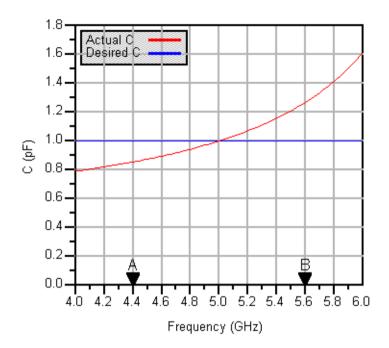

#### **Passive Circuit DG - RLC**

MICapP (Microstrip 4-port Interdigital Capacitor) MICapPG (Microstrip Grounded 2-port Interdigital Capacitor) MICapSG (Microstrip 2-port Interdigital Capacitor) MICapSG (Microstrip 1-port Interdigital Capacitor) MREInd (Microstrip Elevated Rectangular Inductor) MRInd (Microstrip Rectangular Inductor) MSInd (Microstrip Spiral Inductor) MTFC (Microstrip Thin Film Capacitor) TFC (Thin Film Capacitor) TFR (Thin Film Resistor)

#### **Passive Circuit DG - Couplers**

BLCoupler (Branch-Line Coupler) CLCoupler (Coupled-Line Coupler) LCoupler (Lange Coupler) RRCoupler (Rat-Race Coupler) TCoupler (Tee Power Divider) WDCoupler (Wilkinson Divider)

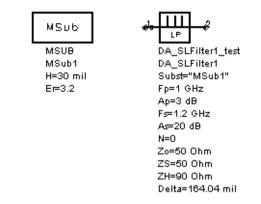

#### **Passive Circuit DG - Filters**

CLFilter (Coupled-Line Filter) CMFilter (Comb-Line Filter) HPFilter (Hairpin Filter) IDFilter (Interdigital Filter) SBFilter (Stub Bandpass Filter) SIFilter (Stepped Impedance Lowpass Filter) SLFilter (Stub Lowpass Filter) SRFilter (Stepped Impedance Resonator Filter) ZZFilter (Zig-Zag Coupled-Line Filter)

#### **Passive Circuit DG - Matching**

DSMatch (Double-Stub Match) LEMatch (Lumped Component Match) QWMatch (Quarter-Wave Match) RAtten (Resistive Attenuator) SSMatch (Single-Stub Match) TLMatch (Tapered-Line Match)

## Passive Circuit DG - Lines

#### **MBend (Microstrip Bend Component)**

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zo = desired characteristic impedance, in ohms

BendType = type of bend

Angle = angle of bend (for arbitrary angle/miter bend)

M = miter fraction (for arbitrary angle/miter bend)

- 1. MBend designs a microstrip bend given the substrate, desired characteristic impedance, and bend properties. The design will realize the native MBEND, MBEND2, or MBEND3 components.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. BendType can be Arbitrary Angle/Miter (MBEND), 90 Degree/Miter (MBEND2), or 90 Degree/Optimal Miter (MBEND3). The parameters Angle and M are only used for MBEND realizations. Refer to the discussion of these components in the ADS Microstrip Components documentation for a more detailed description.

- 4. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

### MBStub (Microstrip Butterfly Radial Stub)

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Xin = desired input reactance, in ohms (only one of Xin, Cin, and Lin can be non-zero)

Cin = desired input capacitance, in farads (only one of Xin, Cin, and Lin can be non-zero)

Lin = desired input inductance, in henries (only one of Xin, Cin, and Lin can be non-zero)

W = width of feed line (set to zero if Z specified)

Z = characteristic impedance of feed line (set to zero if W specified)

Angle = subtended angle of circular sector

d = insertion depth of circular sector in feed line

Delta = length added to stub for tuning performance

- 1. MBStub designs a microstrip butterfly radial stub given the substrate, desired input reactance, and stub dimensions.

- 2. The stub is designed by dividing the radial lines into several short segments.

- 3. For proper operation, only one of Xin, Cin, and Lin can be non-zero. If all are zero, the stub is designed to provide an open circuit.

- 4. Refer to the discussion of the MBSTUB component in the Microstrip Components documentation for a more detailed description of the model used for this component.

- 5. The optimization changes the length of the stubs to achieve the desired input reactance.

- 6. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

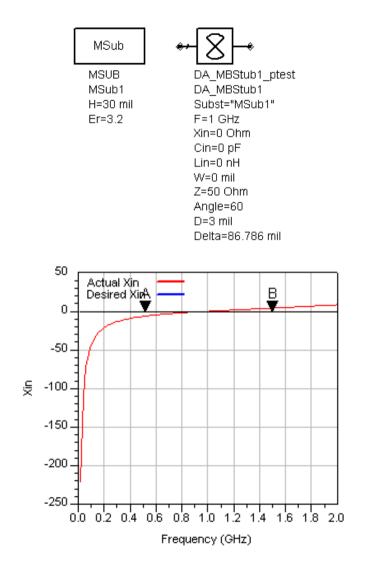

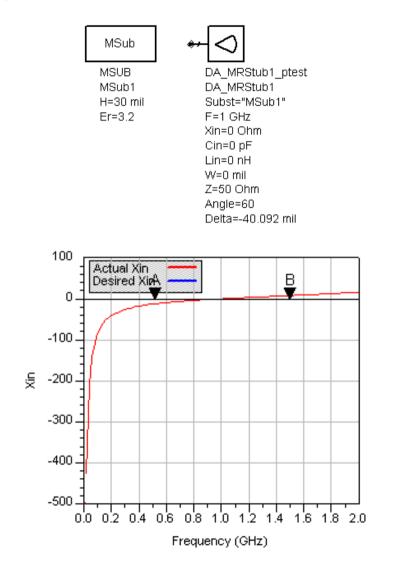

#### Example

A MBStub component was used to design an open circuit stub at a center frequency of 1 GHz. Optimization yielded a value of Delta = 88.786 mil.

## MCFil (Microstrip Coupled-Line Filter Element) Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zoe = desired even-mode characteristic impedance, in ohms

Zoo = desired odd-mode characteristic impedance, in ohms

Zo1 = characteristic impedance of input line at port 1, in ohms

Zo2 = characteristic impedance of input line at port 2, in ohms

Lphys = physical line length (set to zero if Lelec specified)

Lelec = line length in wavelengths (set to zero if Lphys specified)

- 1. MCFil designs a microstrip coupled-line filter component given the substrate, desired evenand odd-mode characteristic impedances, and physical or electrical length.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. For proper operation, either Lphys or Lelec must be zero.

- 4. Zo1 and Zo2 specify the impedance of the lines attached to this component and are provided to ensure proper pin location in the layout. Refer to the discussion of the MCFIL component in the Microstrip Components documentation for a more detailed description of the model used for this component.

- 5. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

## MCLine (Microstrip Coupled Line Component) Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zoe = desired even-mode characteristic impedance, in ohms

Zoo = desired odd-mode characteristic impedance, in ohms

Zo1 = characteristic impedance of input line at port 1, in ohms

Zo2 = characteristic impedance of input line at port 2, in ohms

Zo3 = characteristic impedance of input line at port 3, in ohms

Zo4 = characteristic impedance of input line at port 4, in ohms

Lphys = physical line length (set to zero if Lelec specified)

Lelec = line length in wavelengths (set to zero if Lphys specified)

- 1. MCLine designs a microstrip coupled line component given the substrate, desired even- and odd-mode characteristic impedances, and physical or electrical length.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. For proper operation, either Lphys or Lelec must be zero.

- 4. Zo1 through Zo4 specify the impedance of the lines attached to this component and are provided to ensure proper pin location in the layout. Refer to the discussion of the MCFIL component in the Microstrip Components documentation for a more detailed description of the model used for this component.

- 5. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

### **MCorn (Microstrip Corner Component)**

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zo = desired characteristic impedance, in ohms

- 1. MCorn designs a microstrip corner component given the substrate and characteristic impedance of the input and output lines.

- 2. **Note** A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

- 3. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 4. Refer to the discussion of the MCORN component in the Microstrip Components documentation for a more detailed description of the model used for this component.

### **MCross (Microstrip Cross Component)**

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Z1 = characteristic impedance of port 1, in ohms

Z2 = characteristic impedance of port 2, in ohms

Z3 = characteristic impedance of port 3, in ohms

Z4 = characteristic impedance of port 4, in ohms

- 1. MCross designs a microstrip cross given the substrate, desired characteristic impedance on each port, and bend properties. The design will realize the native MCURVE and MCURVE2 components.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. Refer to the discussion of the MCROSS component in the Microstrip Components documentation for a detailed description of this component.

- 4. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

## **MCurve (Microstrip Curve Component)**

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zo = desired characteristic impedance, in ohms

Angle = angle of curve

Radius = radius of curvature (set to zero if Lelec specified)

Lelec = curve length in wavelengths (set to zero if Radius specified)

CurveType = type of curve

Nmode = number of modes (for Waveguide Model)

- 1. MBend designs a microstrip bend given the substrate, desired characteristic impedance, and bend properties. The design will realize the native MCURVE and MCURVE2 components.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. Either Lelec or Radius must be zero for proper operation.

- 4. BendType can be Transmission Line Model (MCURVE) or Magnetic Wall Waveguide Model (MCURVE2). The parameter Nmode is used only for MCURVE2. Refer to the to the discussion of these components in the Microstrip Components documentation for a more detailed description.

- 5. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

## MGap (Microstrip Gap Component)

#### Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zo = desired characteristic impedance, in ohms

S = length of gap (spacing)

- 1. MGap designs a microstrip gap given the substrate, desired characteristic impedance, and gap width.

- 2. Since the design uses the models inherent to ADS to compute the line width, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. Refer to the discussion of the MGAP component in the Microstrip Components documentation for a detailed description of this component.

- 4. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

## MLine (Microstrip Line)

Symbol

#### Parameters

Subst = microstrip substrate name

F = design frequency, in hertz

Zo = desired characteristic impedance, in ohms

Lphys = physical line length (set to zero if Lelec specified)

Lelec = line length in wavelengths (set to zero if Lphys specified)

- 1. MLine designs a microstrip line given the substrate, desired characteristic impedance, and physical or electrical length.

- 2. Since the design uses the models inherent to ADS to compute the line width and length, there is no need for a dedicated Simulation Assistant, Optimization Assistant, or Display Assistant.

- 3. For proper operation, either Lphys or Lelec must be zero.

- 4. Refer to the discussion of the MLIN component in the Microstrip Components documentation for a more detailed description of the model used for this component.

- 5. A SmartComponent subnetwork is empty until the Design Assistant is used to generate the design. Refer to "Design Assistant" on page 3-1.

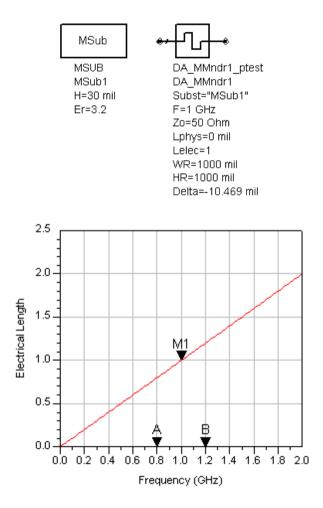

## MMndr (Microstrip Meander Line)

Symbol

#### Parameters

Subst = microstrip substrate name

- F = design frequency, in hertz

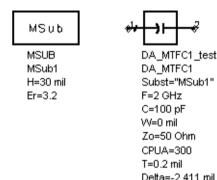

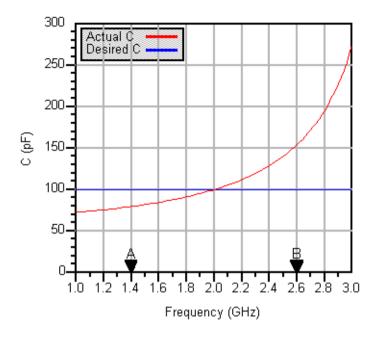

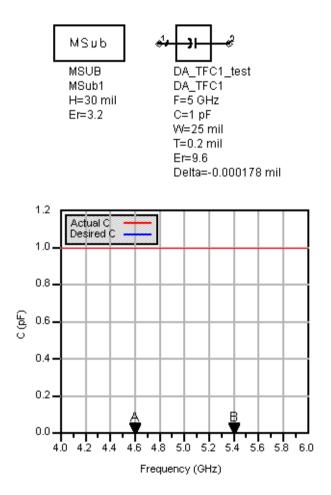

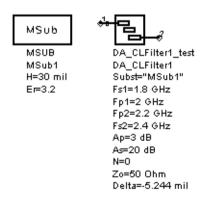

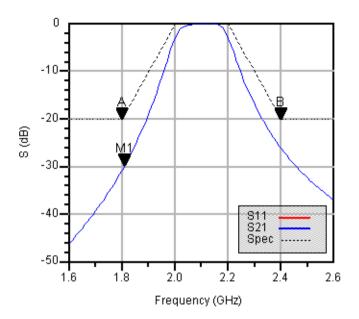

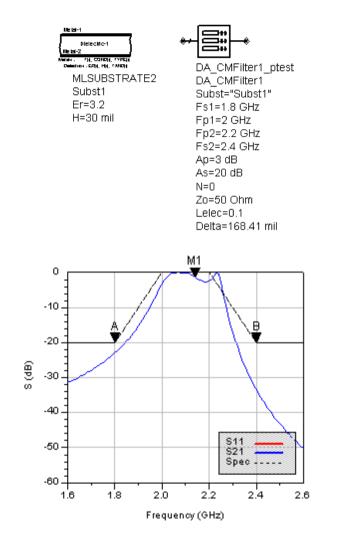

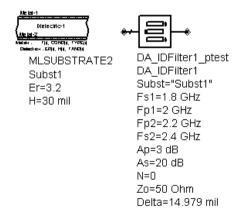

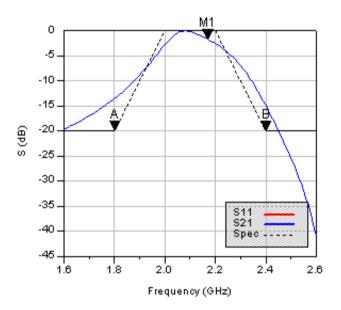

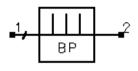

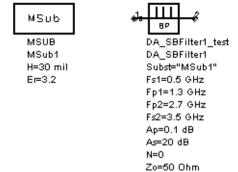

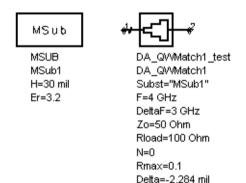

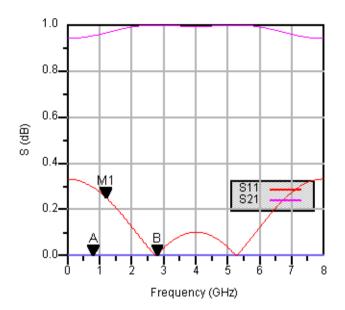

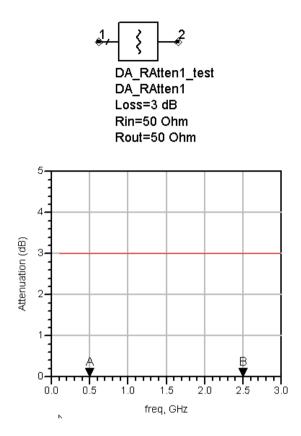

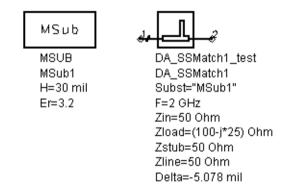

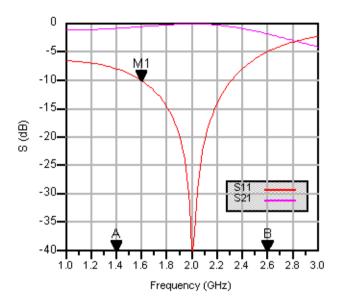

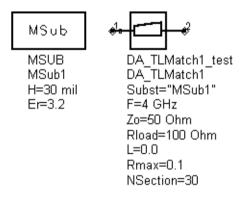

- Zo = desired characteristic impedance, in ohms