- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Simulating LVDS with STRATIX4 ibis in CST design studio

录入:edatop.com 点击:

Hello,

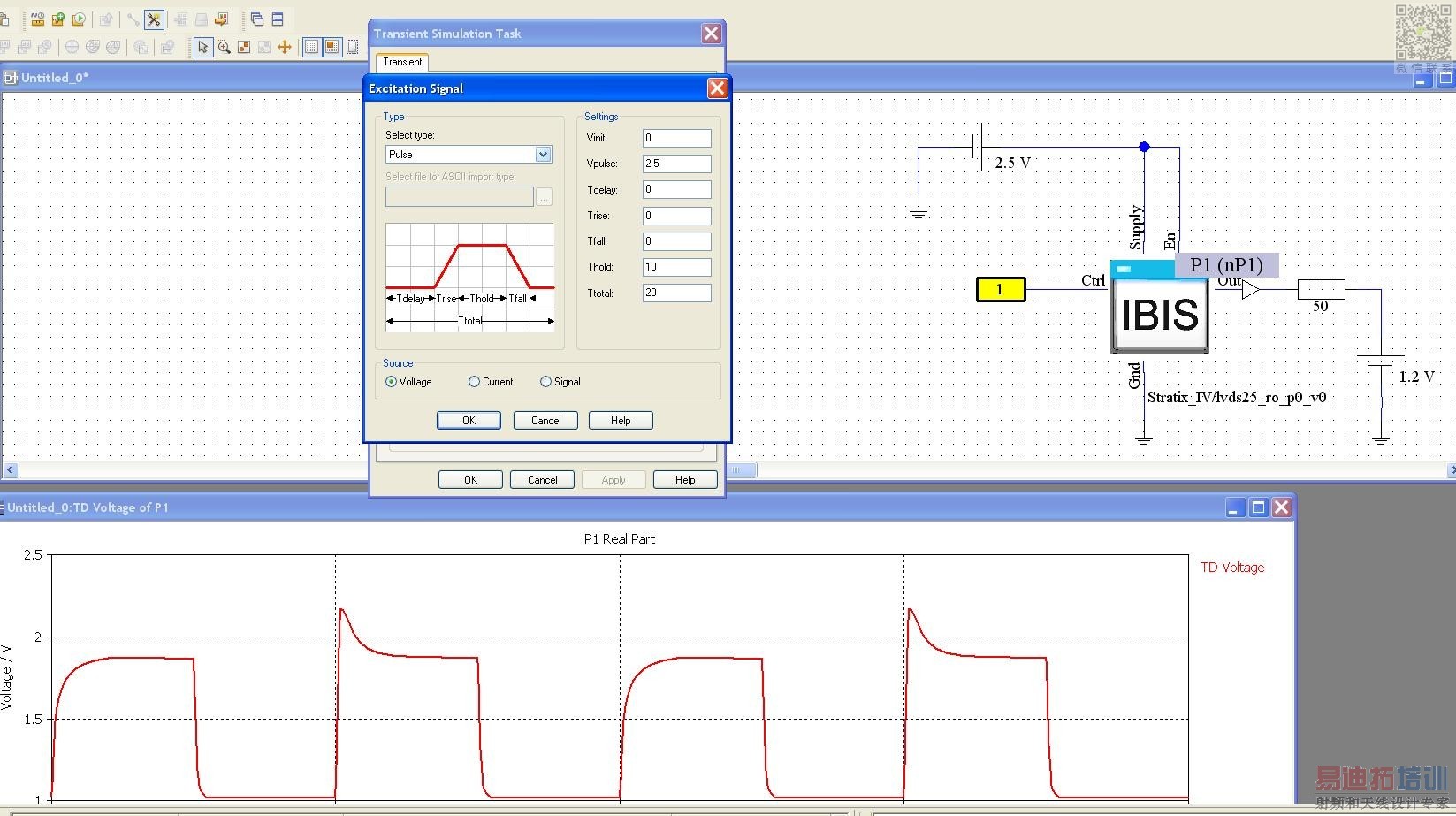

I am trying to do simulation of a single net in an lvds pair with CST design studio. The outputbuffer-ibis model used is the following: lvds25_ro_p0_v0 which can be found in the attached ibis model of the altera stratix IV device. (Stratix4.zip)

My setup in CST can be found in the attached LVDS.jpg

To simulate the single ended net in CST, I terminated the output with a 50Ohm resistor to Vfixture, which is 1.2V.

The excitation signal on the ctrl pin of the ibis block is defined as 50MHz with a voltage level of 2.5V. But I am not quite sure if this is correct... I would expect that the voltage levels, and rise/fall times would come out of the ibis outputbuffer block... I connected also the Supply and En pin of the IBIS block to 2.5V. I also don"t know if this is correct.

Then at the bottom of the image, you can find the simulated waveform at the output... This is really not what I expected... I expected a voltage waveform of 50Mhz (this is correct) with Vol = 1V and Voh = 1.4V. And also the waveform is not uniform, I have an overshoot every other pulse.

Any suggestions?

Thx,

Tim

I am trying to do simulation of a single net in an lvds pair with CST design studio. The outputbuffer-ibis model used is the following: lvds25_ro_p0_v0 which can be found in the attached ibis model of the altera stratix IV device. (Stratix4.zip)

My setup in CST can be found in the attached LVDS.jpg

To simulate the single ended net in CST, I terminated the output with a 50Ohm resistor to Vfixture, which is 1.2V.

The excitation signal on the ctrl pin of the ibis block is defined as 50MHz with a voltage level of 2.5V. But I am not quite sure if this is correct... I would expect that the voltage levels, and rise/fall times would come out of the ibis outputbuffer block... I connected also the Supply and En pin of the IBIS block to 2.5V. I also don"t know if this is correct.

Then at the bottom of the image, you can find the simulated waveform at the output... This is really not what I expected... I expected a voltage waveform of 50Mhz (this is correct) with Vol = 1V and Voh = 1.4V. And also the waveform is not uniform, I have an overshoot every other pulse.

Any suggestions?

Thx,

Tim

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习易迪拓培训专家讲授的CST视频培训教程。

上一篇:cst waveguide studio+video

下一篇:hfss or cst how to include a black box with specific s parameters in the whole design