- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CST MWS Coupled Microstrip波导端口设置求助 EDATOP请进

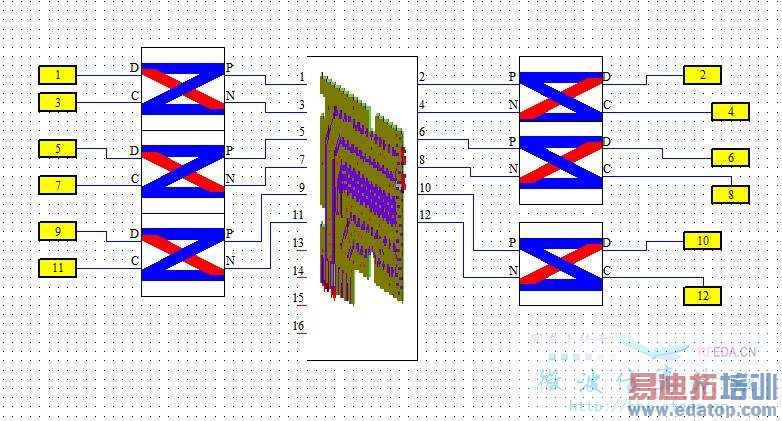

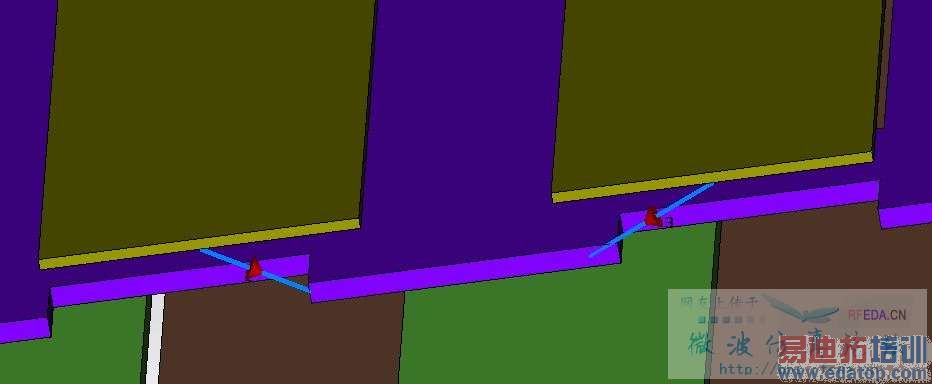

现在想仿真图中Port1对Port5, 和Port1对Port3的NEXT. 同时也要查看SCD21,SDD21等参数.

模型看了一下,不明白为什么要把网格设置得那么小,光是预设置那些就花了快40分钟,45分钟的是候没看到有unstable,我就先停了,等不起。

关于端口提示inhomogeneous,这个是由你的模型决定的,端口处除了信号耦合微带线,两侧有地,中间有介质,上面有空气,肯定inhormogeneous。

如果是warning,在可以证明不影响最终结果的前提下,可以忽略。

耦合微带,差模激励条件下设计的阻抗是多少?97或者40哪个更接近就说明另一个很可能是错误的结果。

关于离散端口,如果仿真目的是看NEXT、TCL和IL,如果模型尺寸已经固定,看端口阻抗的意义是什么?

谢谢老大这么晚还来解答!

网格的设置是用的CST里 EDA template的网格设置. 初学CST。还请多多指教.

耦合微带,差模激励条件下设计的目标阻抗是100ohm. 但是现在由于Pad 的宽度和间距限制(尺寸已经不能更改). 阻抗是在40ohm.用阻抗计算软件也是在40ohm.

所以只能挖空下面的GND去提高阻抗..挖空之后.阻抗是在97ohm.,但是无法仿真.

1. 对于这样的结构,可否用Mulitpin 波导端口去做仿真?

2. 如可以,端口大小该如何设置? 如果按照10H, 和10W,去设置, 两个相邻的端口会有叠加。 导致不能仿真.

3.用离散端口后,发现Return loss会比较大,所以想去看看端口阻抗是否匹配.

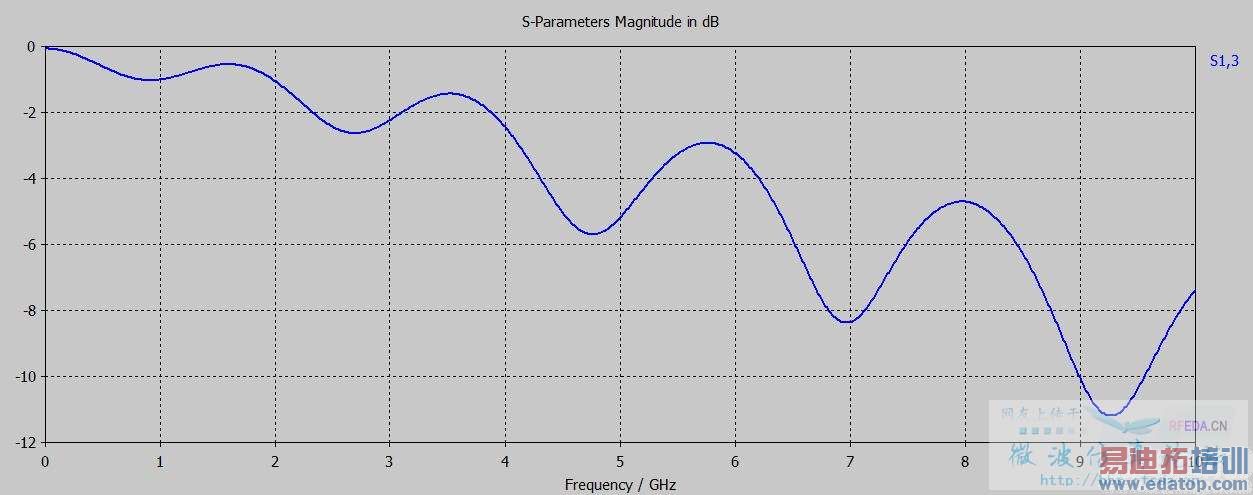

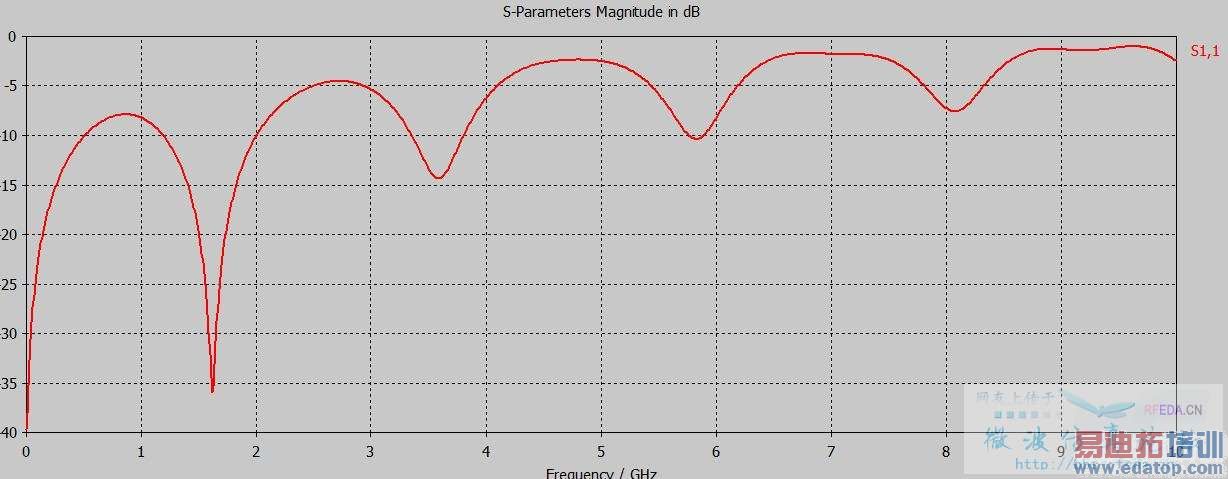

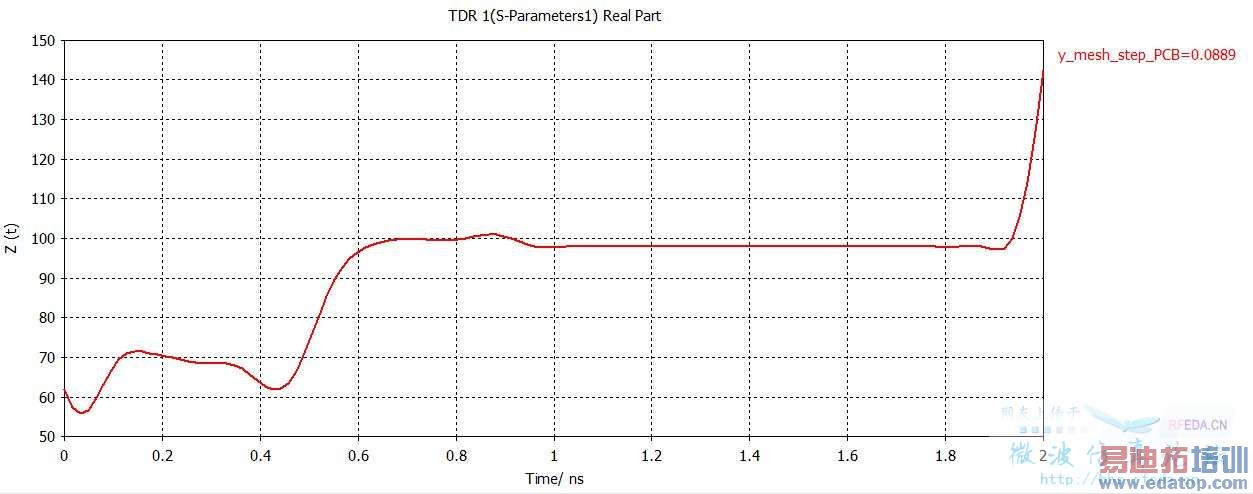

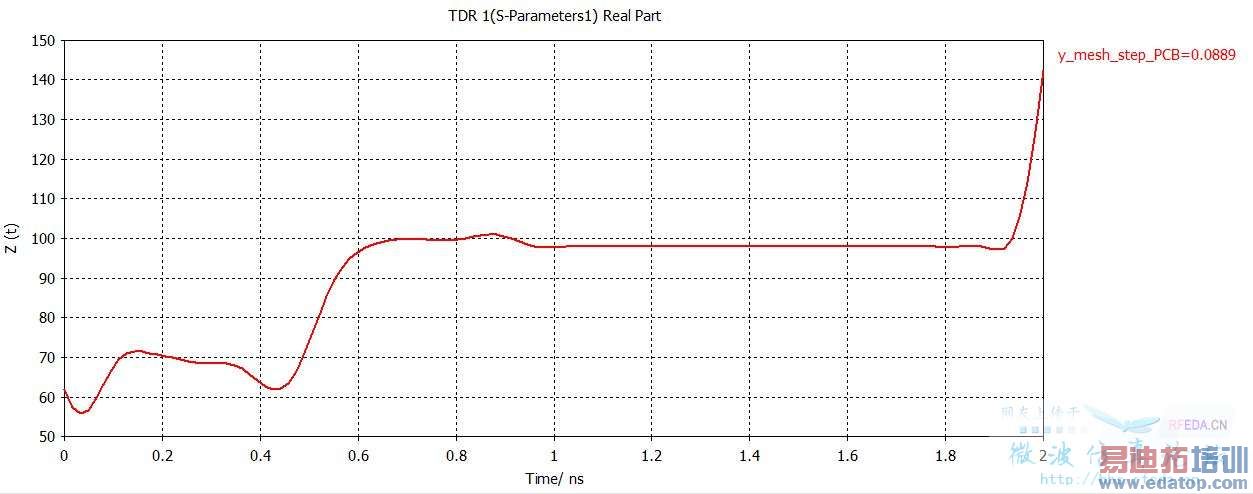

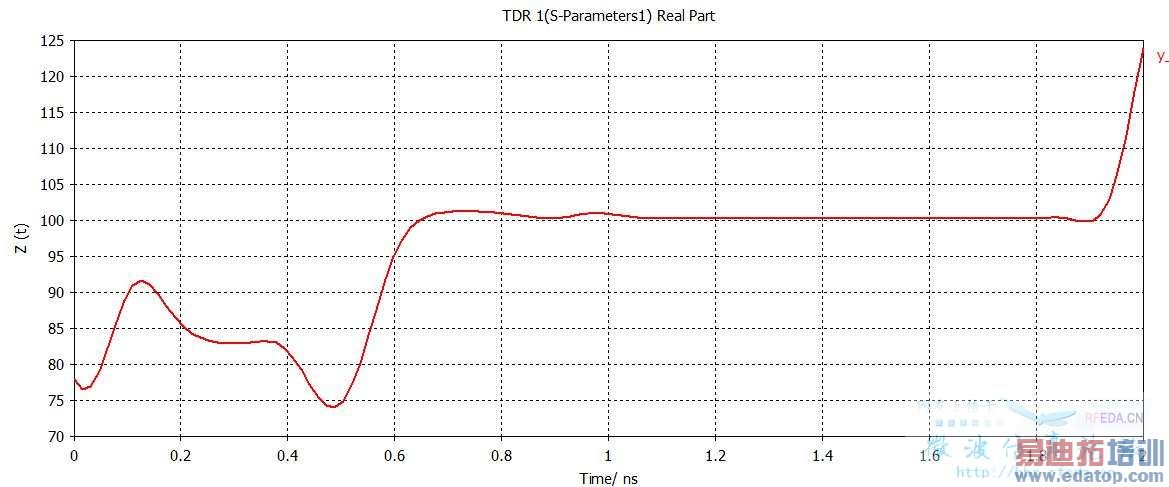

下面是离散端口的结果。

从Time from S 参数.的TDR, 阻抗的起点60ohm, 和波导端口差异较大,不知道以那个为准.还请帮忙看看.

你的Mesh line ratio limit设置成100,因此minimum mesh step只有0.01,会导致仿真速度极其缓慢。CST MWS帮助文件《Transient Solver Performance Improvements》。

理论上Multipin Waveguide Port是最适合做这种仿真的,但是如果端口处模型太复杂,或者模型已经不具备Multipin waveguide port设置共模模式,那么就只能考虑离散端口。

离散端口的结果是用在哪个模型里的,40还是97?离散端口的端口阻抗是多少?

Mesh line ratio limit已经设置为10。10,,10 的参数.

40和97都有试过.

1.40ohm

2. 97ohm

离散端口需要在RUN完S参数后,才能知道阻抗。 可否先通过其它办法先计算阻抗

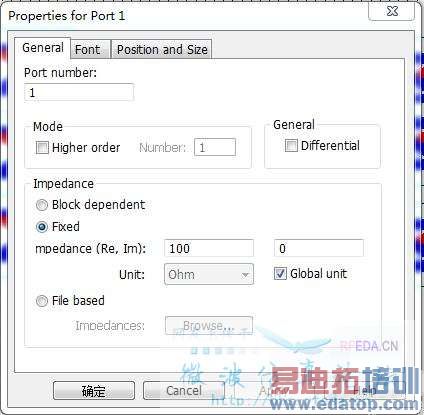

离散端口的端口阻抗是50ohm. DS 里的为100ohm.

没看明白是什么意思。如果设计的阻抗是100,为什么离散端口不用100?

离散端口是怎么接到模型上的?DS的连接图是什么?

离散端口阻抗50

连接图

连接图中port1 的差模为100ohm。共模为25ohm。

离散端口接法

不挤牙膏了,要不然会一直挤下去的……

如果关心的是“为什么离散端口计算得到的TDR起点端口阻抗和波导端口的结果不一致”,那么楼主为什么觉得他们必须是一致的?

假设仿真一个很“正规”的传输线结构,用离散端口和波导端口计算得到的TDR一致吗?我不知道答案,楼主知道吗?

这个真的不太清楚.

那我将离散端口的TDR起点端口阻抗通过挖铜的方法调到100ohm(因DS里差模设置为100ohm,测试系统也是100ohm),是否会对Return loss有较好的匹配?

1,如果我用离散端口的话。可否先知道阻抗是否已经调节OK, 不用去跑S参数后才能知道, 不知道老大有没有什么好的办法.

2.如果离散端口的起点调节到100ohm. 是否和实际测试的值接近,或者误差很小.

老大,现在很迷茫,还请多多包涵。

谢谢先

我很少研究TDR,所以不了解TDR方面的相关知识。只不过经验中离散端口和波导端口方针传输线结构在低频部份不一致,不确定对时域方面的影响是什么。

关于输入阻抗,可以把模型简化为纯耦合传输线,用波导端口就可以计算mode properties,得到line impedance。

关于实测,我没有测过TDR,不了解起点调节到100的意义是什么。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习易迪拓培训专家讲授的CST视频培训教程。

上一篇:SAT格式的文件,是一个贴片天线,导入CST中,如何找到它的馈电点?

下一篇:在CST MWS中用VBA修参数后,怎么实现“自动点击”那个F7啊,