- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CST MWS阻抗仿真问题

看不懂描述……

新手进来学习下。

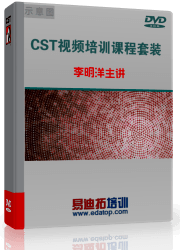

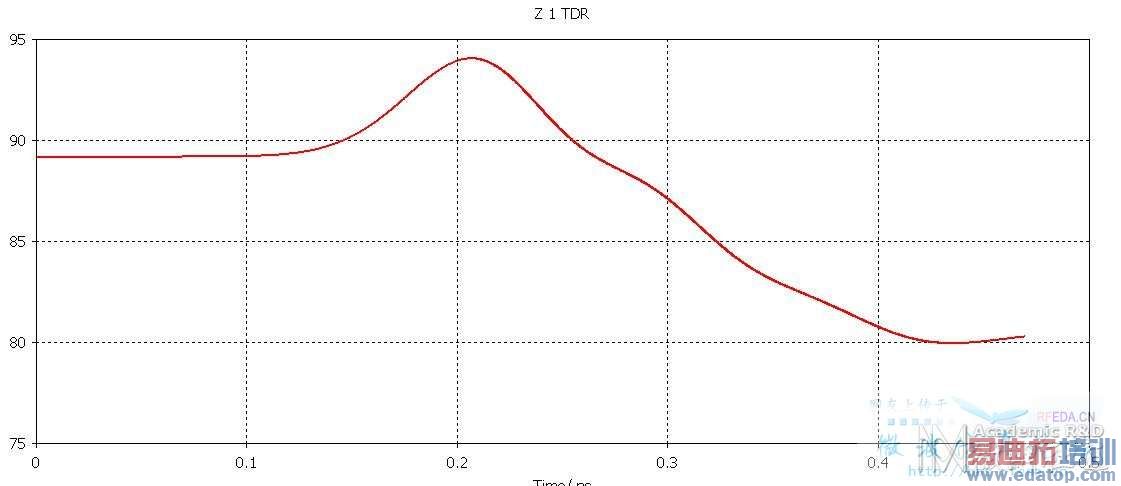

端口1阻抗88,端口2阻抗93;PORT1正常的阻抗分布图应该是:在图1后面80处上升至93就是接上图2那部分,才是整个通路的阻抗分布;但实际仿真出的结果只有图示的这一部分,请帮忙看下原因,谢谢!

还是不知道你做的是什么东西,也不理解阻抗分布图为什么是你描述的那样,更不理解为什么仿真出来的和你预想的不一样。总而言之,依照你已经提供的信息,以我个人的智商,我猜不出来原因。

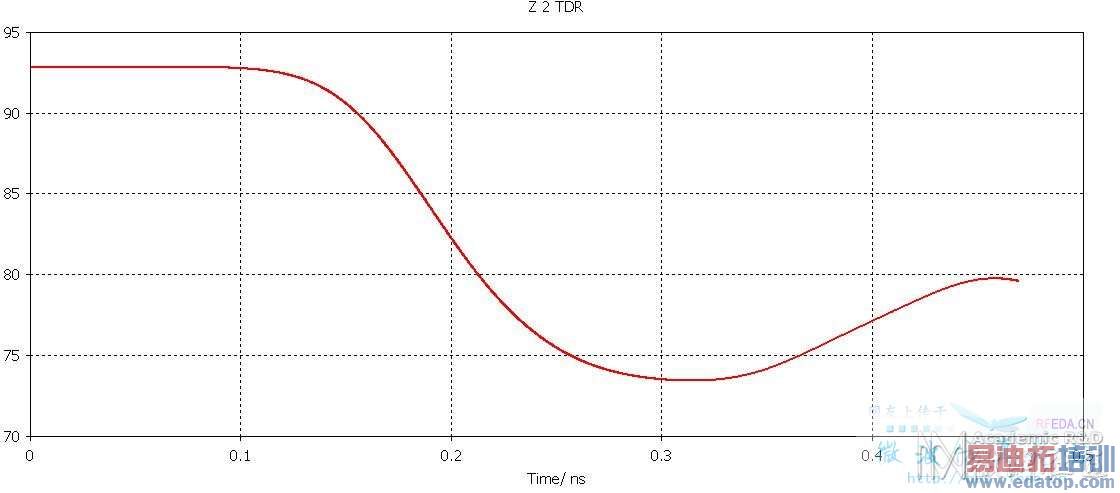

为了更好的说明问题,我再发一个图,图3是我根据仿真情况合成的模拟图。我仿真的是一段通路的阻抗,正常的阻抗分布应该是图3这样的趋势,因为PORT1阻抗为88,PORT2阻抗为93,所以正常的阻抗分布图应该是图3这样的趋势。而实际的结果是PORT1的阻抗只有图3的左边PORT1端,PORT2的阻抗只有图3的右边PORT2端,就是仿真结果没有表现出整个通路的阻抗分布!再次求助,分析可能的原因,谢谢!

重复4楼的话,别人不知道你的模型是怎么建立的,你的问题很难回答。所以至少应该描述一下你的模型结构吧?以及仿真相关的参数设置,仿真流程细节,后处理模版的选择等等。最简单的办法就是上传模型文件。

那我发下模型,劳驾版主看下!

哪位看过模型的高手给我老人家说说看这个模型是什么样的?

哎,我来替你做你该做的事情吧:

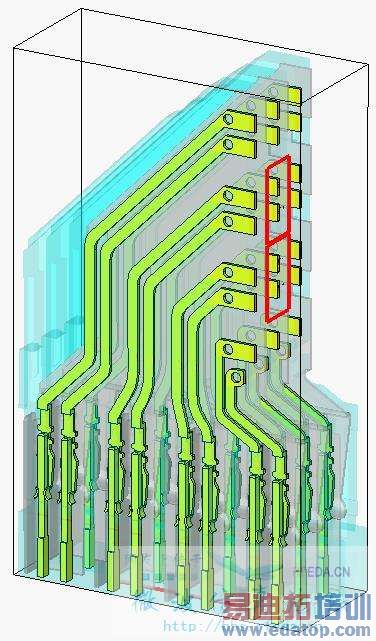

模型截图:

一个connector性质的器件,导体是Brass金属,外包带损耗的介质材料LCP(Epsilon=3.2),每个分结构侧面有PEC建模的类似挂钩的东西。

用multipin wavegguide port创建了四个端口,每个端口只设置差分模式……。

仿真频率0 - 10 GHz,边界条件conducting wall。

Transient Solver Accuracy: -20 dB……,Normalized to 100 ohm impedance, 选了Adaptive Mesh Refinement,使用Expert System……。

Global Mesh Properties: 10, 10, 10,Edge refine factor: 5,所有的copper使用local mesh properties: 0.1, 0.1, 0.1……。

后处理模版调用"TDR from Time Signal",端口1和2都使用默认设置。

楼主的问题:理论的“通路”阻抗应该是5楼显示的那张模拟图,实际通过CST MWS后处理计算得到的Port 1的阻抗只有Port 1的部分,不包含Port 2的部分;同样,通过CST MWS后处理计算得到的Port 2的阻抗只有Port 2的部分,不包含Port 1的部分。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习易迪拓培训专家讲授的CST视频培训教程。