- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请指点排错思路:the port is excited below its cutoff frequency

请让我一次问个够。

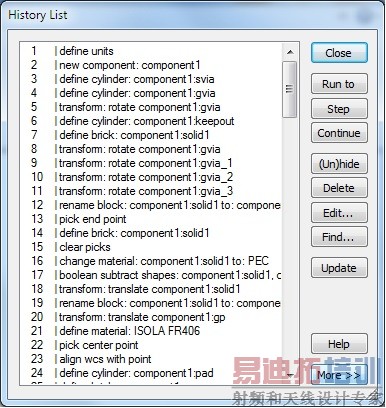

CST 2015自带的教程里面有个via的model,我不懂:

1、slice by uv plane这条命令的作用(help文档中没有找到相应的帮助);

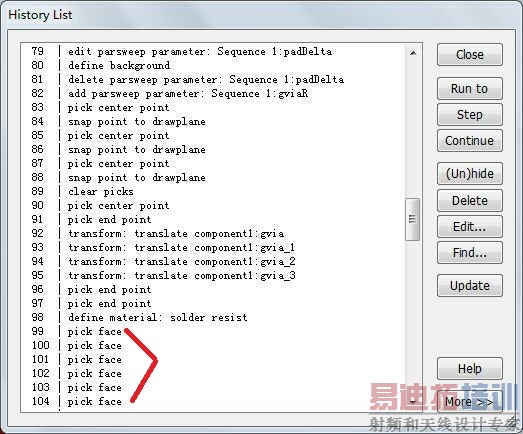

2、我查看了步骤,为何在6步pick the face操作后生成一个solid1?这条命令能不做吗?

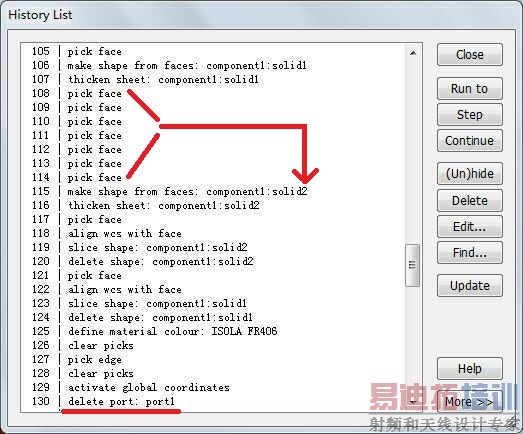

3、为何总是定义了port1port2后又删除?我看到history tree里面有两次这样一样的建立了又删除了的操作步骤,不知用意何在;

4、port2能否不加?

以上,多谢多谢!

自己先回答cut-off frequency的定义,再把提示你的这句话翻译成汉语。

1. 沿着uv平面分割选中的模型。CST MWS帮助文件《Structure Editing Overview》。

2. 不知道你说的是哪个via model。唯一能找到的via connection模型第6步和你说的不一样。

3. 同上。

4. 不加port 2的话,port 1激励时负载是什么?

1、the port is excited below its cutoff frequency的意思我认为是激励信号的频率低于端口的截止频率,所以出现错误。但是就我的模型而言,1D Result显示端口截止频率很高,而我不可能设置比这还高的频率的激励信号,所以,我是想问采取什么措施可以如何降低端口的截止频率呢?

2、via model的教程目录:help--contents--example and tutorials--cst wms example--tutorials--overview--signal integrity: simulation of a via model受累帮我看一下吧,感谢!

如果你确定能在1D Results里看到cut-off frequency的话,说明你使用了不合适的器件去做它做不了的事情。那么这和软件无关,这是你的设计问题。至于怎么降低,你需要自己学习微波原理。

这个模型的第6步不是pick the face,第7步生成的solid1就是整个器件的substrate,你自己觉得可以不要吗?

所有125个步骤里没看到有任何删除端口的操作,所以你打开的这个模型一定被别人“玩儿”过了。

1、首先非常感谢您能帮助我这个菜鸟。

2、是我写错了,是2D Result————port mode下查看的Fcutoff。我翻书找到了平行平板波导TM模的截止频率计算公式,但是将平板间距0.254mm, 电导率磁导率参数都代入公式,求得的截止频率反而很小。显然不对

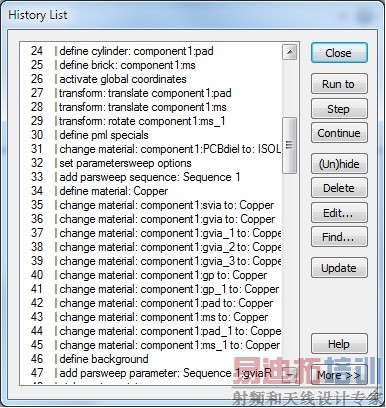

3、我用的CST2014,via model的history tree特意截图(我肯定没被人改过),烦请看一下。我认为solid1不是衬底,PCB diel才是。solid1是将上表面的微带线,焊盘,还有PCB diel的顶层打包在一起了,但不知用意。

多谢多谢!

1. 不客气。

2. 要么公式是错的,要么计算是错的。

3. 我只有2015版的,没看到任何delete 端口的操作。

4. 至于选中7个面创建shape,我最开始理解错了,以为是整个模型创建历史的第6步和第7步。如果你有心看一看component tree,或者第107步,这个结构的材料叫做solder resist。如果你第一次听说这个词,去网上找它的解释,就应该知道这是在做什么以及为什么要这样做。

我看到过solid1是solder resist这个材料,只是当时我想着solid1里面选到的焊盘,微带线不都应该是PEC或者copper材质的嘛?没去想实际是在这些选中的component的face上涂上了绿油。感谢您还帮我截了图,非常感谢您的帮助!

好东西,我来看看,多谢 ,好东西,我来看看,多谢

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习易迪拓培训专家讲授的CST视频培训教程。

上一篇:antenna magus怎样获得?

下一篇:CST探针的作用