# AWR Delivers Faster Interconnect Modeling and Analysis with Innovative ACE Circuit Extraction Technology

#### By Dr. Michael Heimlich, Applied Wave Research, Inc. Introduction: Where Did Engineering Design go?

The traditional approach to microwave and RF circuit design — the present day foundation for high-frequency wireless designs — is being pressured simultaneously by an increase in operating frequencies/bandwidth and a decrease in overall circuit size/ dimensions. The result is that the physical design challenges faced by circuit designers are rapidly increasing, while choices in how these challenges should best be addressed are not.

Communications designers developing products with GHz frequencies and Gbps edge rates who are using traditional printed circuit board (PCB) signal integrity (SI) solutions are finding that while their designs behave well under virtual prototype or simulation scenarios, they are failing when migrated to build and test. Why? Because the design of the interconnects above 1 GHz is an increasingly important issue — no longer a second-or third-order effect that can be largely ignored. Due to both large-scale integration and higher operating frequencies, interconnects no longer operate as simple lumped RLC circuits and so, the modeling and simulation of these high-performance and complex design interconnections must be taken into account right from the beginning. Designers who do not do this are finding themselves spending excessive time and money on redesigns and re-spins, and experimenting on the test bench, which adds cost to the final product not only in additional "fix-it" components, but ultimately also in lost market window opportunities.

CKT CAP 12 ID="1" C=4.5333e-002 11 Er=4.38 H=250. T=27. Rho=0.86281 MSUB Tand=2.5e-002 ErNom=4.38 Name="SUB21" 12 ID="3" W=160. L=80. MSUB="SUB2 Er=(3.5,4.6) Tand={2.5e=002,1.7e=002} MLIN 14 MSUB="SUB21" H={50.,200.} GMSUB N=2ErC=1. HC-700. HB-0.25 T-{27.,27.} Rho=0.86281 Cover-1 Gnd-0 TandC-0. Name="SUB24" SW-0. SWRight=0. SigmaC=0. Sigma={2.5e-002,1.7e-002} RhoV-{0.86281,0.86281} 8 TD="6" N=2 GMCLIN 3 14 L=2270, Acc=1, GMSUB="SUB24" 1 FileName="" SaveToFile=0 W1=160. W2=160. Offs1=0. Offs2=320. CL1=1 CL2=2 Er=4.6 H=200. T=27. Rho=0.86281 MSUB Tand=1.7e-002 ErNom=4.6 Name="SUB25" ID="8" W=160. L=240. MSUB="SUB25" MLIN 11 7 ID-"10" N-2 GMCLIN 15 10 2 L-2560. Acc-1. GMSUB-"SUB24" ID 4 2 ID-"10" N-2 L-2560. A SaveToFile=0 FileName="" W1=160. W2=160. Offs1=0. Offe2=360. CL1-1 CL2-2 MLIN 15 ID="11" N=160. L=80. MSUB="SUB21" 12 MBENDR 7 ID-"12" W-160. MSUB-"SUB25" 8 11 ID-#13" W-160. L-280. MSUB-#SUB25" MLIN 0 ID="14" W=160. MSUB="SUB25" MBENDR 9 10 DEF4P 1 2 3 4 ExtractedNetlist

Figure 2: A netlist created in ACE representing interconnects in Figure 1

ACE<sup>™</sup>, an innovative circuit extraction technology now available in the Microwave Office® 2007 design suite from Applied Wave Research, Inc. (AWR®), was developed specifically to deliver productivity benefits to the designers of today's complex, nextgeneration communications products. This novel circuit extraction design approach dramatically reduces from hours to seconds the time required to perform the initial modeling of complex interconnects. In addition, it enables the designer to integrate interconnect modeling at the earliest stages of the design flow, where problems can be identified and corrected before costly and time-consuming redesigns are required. These benefits deliver a higher degree of confidence in less design cycle time, ensuring that products will be volume manufacturable, cost-effective, and timely.

The AWR circuit extraction technology enables Microwave Office users to leverage layout-based models for circuit extraction as opposed to traditional schematic-based designs/flows. It provides a dramatic and revolutionary methodology shift to layoutdriven simulation through a sophisticated mechanism for automating the bookkeeping and partitioning of structures into pre-existing models. The introduction of this technology is ground-breaking in that productivity is enhanced further through the use of AWR's Intelligent Net<sup>™</sup> (iNet) schematic-layout interconnect automation technology. This capability is ideal for RF/microwave designs where the modeling of interconnects is not well-suited to traditional circuit-based approaches, or where the interconnects are parasitic and dense, yet critical to overall product performance. The ACE technology, which is similar to parasitic extraction techniques for digital and analog designs, is orders of magnitude faster than the traditional EM methods normally used for RF/microwave interconnect extraction because it groups interconnects together and effectively creates a schematic model using distributed and coupled-line circuit elements. Similarly, rather than using generalized finite element method (FEM) or method-of-moments (MOM) solvers designed for arbitrary arrangements of geometries, many of these circuit elements leverage highly optimized EM solvers, providing a tremendous speed advantage.

## What is ACE?

ACE, at its heart, would be described as a circuit extractor by most of the digital and analog-mixed signal design community. The technique is not well-known to the RF/ microwave world because it has traditionally been used with RC models of the interconnects — corresponding to a low-frequency view of interconnects. The ACE software's breakthrough is to combine high-frequency sensibilities in the way the geometries are viewed by employing proven distributed models from many years of successful microwave and millimeter-wave designs.

Inherent in the technology is a necessary awareness of the current return path. Lowfrequency extraction techniques nominally ignore the consideration of a "ground" and leave it up to the user or simulator to determine current return paths after the fact. The consequence of such an assumptive approach is that the result is unreliable or unrealistic. The ACE software inherently understands the current return path and incorporates it automatically in the generation and selection of multiple substrate definitions for the same integrated circuit (IC), module, or PCB technology.

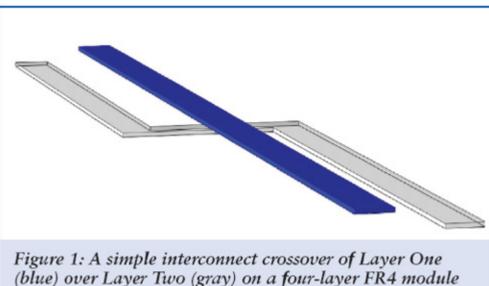

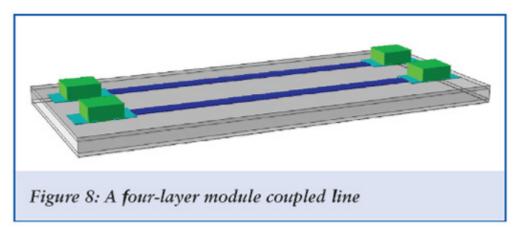

Unlike traditional EM solvers, the ACE technology creates frequency-dependent circuit models from geometric structures without the need to directly solve Maxwell's equations. Coupled multi-layer lines (**Figure 1**) are analyzed for their length, width, layer, and position of each segment relative to every other segment on all the other lines.

Based on user-specified criteria, this analysis generates a circuit-based netlist (**Figure 2**) containing distributed models for all of the interactions among the interconnects: coupled lines, discontinuities, cross-overs, vias, and independent segments. The speed improvement over the traditional method of directly solving Maxwell's equations with a generalized three-dimensional (3D) volume or planar solver is dramatic — as much as 1000x or more — because the solution is first approached through reducing the complexity geometrically by identifying coupled-line configurations and other grouped structures. Modeling of these structures can then be performed with optimized EM solvers in critical areas. The accuracy is determined by the models to which the geometric structures are mapped and the applicability of the user-selected criteria for issues such as coupling distances and minimum line lengths. These models are useful in linear and nonlinear frequency-domain simulation as well as time-domain simulation, such as HSPICE.

### **RF-style Schematic**

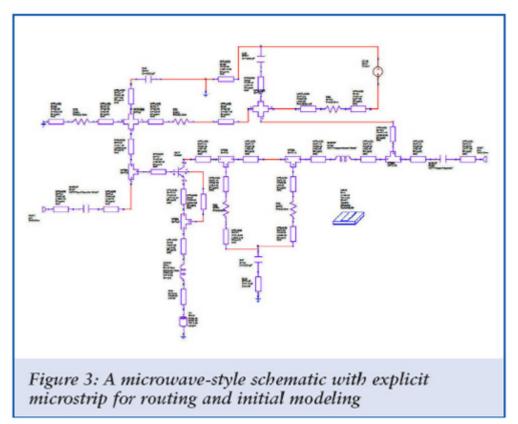

Typical RF/microwave designs would explicitly define all of the interconnects in the schematic, as shown in **Figure 3**.

This approach requires significant effort on the part of the user, not only to capture the schematic topology, but also to ensure that each line length, bend angle, etc. is accurately accounted for and represented in the layout. While this enables the use of distributed circuit modeling (microstrip and stripline lines, bends, discontinuities, etc.) in order to obtain first-order performance of the interconnects, it ignores the coupling and parasitics. Initial distributed effects are easily captured in this approach, but finding all of the couplings becomes a bookkeeping nightmare, especially as segments are often added to individual routes later in the design.

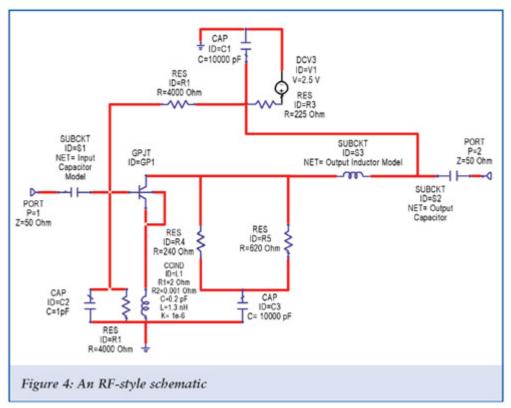

In another approach, many designers forgo this step and go straight to layout, expecting to generate an extensive and intensive amount of EM-layout iteration in order to achieve the right design. In this case, the designer has already decided the metal is not driving the overall circuit performance and is simply parasitic. The corresponding schematic contains no distributed elements in the interconnects (**Figure 4**). The design achieves the second-order couplings much more quickly than in the former approach, but the primary effect of the interconnects must wait until the entire circuit is run through a generalized EM solver late in the design flow process, where work-arounds and fixes are more costly and time-consuming to make.

For the case of a microwave-style design, the user must input all the microstrip-stripline explicitly. AWR's ACE software effectively eliminates this requirement with the mechanization of routable, meandered microstrip lines, including curved, mitred, or differential. Even with this automation, however, the schematic is still cluttered with elements whose sole purpose is to route lines. But what happens when there is significant interconnect coupling such that inputting coupled line models adds so much more complexity to the situation that the designer can't see where all the couplings are?

## Layout Automation and Incremental Modeling

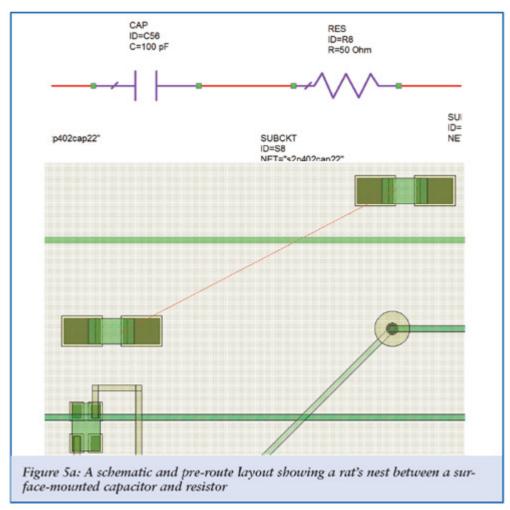

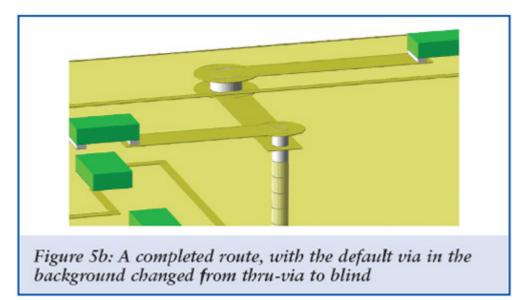

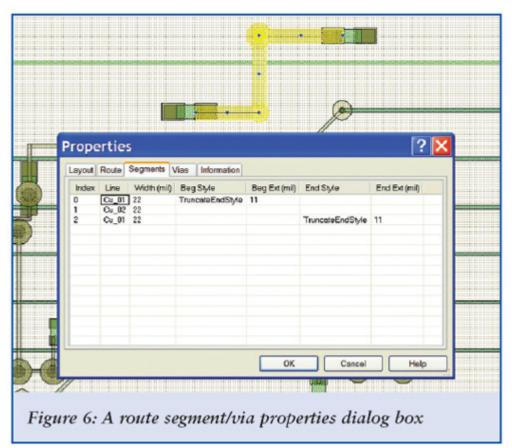

AWR's iNet technology is used to automate layout implementation of the interconnects, as represented on the schematic by wires. A layout net, represented as a rat's nest, is selected in the layout and then routed (**Figure 5a**). The user simply clicks the path from component to component and the line is routed using specified default vertical and horizontal routing layers and widths (**Figure 5b**). Layers are changed by rolling the mouse wheel, and route widths and via types can be changed globally or segment-by segment. Vias are generated automatically in any technology — RFIC, monolithic microwave IC (MMIC), PCB, low temperature co-fired ceramic (LTCC) — by parametric cell generators using technology-specific, design-rule-correct data from the user. Typically, iNet routing takes less than one-tenth the time of explicitly defining microstrip lines, bends, crosses, and tees, and about one-half the time as using paths and manually-inserted vias. The ACE method can be used on the single route (**Figure 3**), the completed design (**Figure 6**), or anywhere inbetween at any stage of the design, as demanded by the evolution of the design and the user.

In other words, the ACE technology can be applied at any time during the formation of the schematic; the user does not need to wait until the design is completed, captured, and laid out. Small sections of the design, such as bias circuitry or control lines, can be analyzed individually and then combined with larger portions of the design as it matures. Structures previously modeled by ACE can be instantly re-analyzed during final design verification with any EM solver connected to AWR tools through AWR's EM Socket<sup>™</sup> open industry standard interface for the direct integration of popular EM solvers into the AWR design environment. The iNets' automation and EM Socket open integration speeds design completion because all EM solvers can share the same structures that the ACE software uses; going from ACE to any EM solver simply requires "clicking" to select the solver(s) of choice.

### **Flexibility of Model**

Mapping of geometric structures to appropriate circuit models in the ACE software can be specified to tune for accuracy and speed. The technology operates fastest when it does not use any models with built-in EM solvers; in this mode it uses traditional closed-form models for microstrip and stripline couplings. Changing from closed-form models to EM quasi-static models improves accuracy, but takes additional time, as the ACE product now maps coupled line structures into AWR's specific model set, which is capable of modeling all practical coupled line configurations using built-in EM quasi-static analysis. The 2D cross-sectional EM solver inside this model is solved at one frequency point and then scaled over the entire frequency range. The ACE technology is most accurate when used with AWR's model set that employs FEM techniques solved at each frequency.

Other geometric structures can be similarly controlled. Junctions and discontinuities can be modeled with closed-form models, such as T-junctions. If greater accuracy is required, AWR's X-models can be used, providing EM accuracy at circuit-model speed by using pre-calculated EM-based tables for the specific arrange of dielectrics in the design.

Vias can be explicitly modeled in numerous ways. S-parameter files from measured or simulated data can be specified for each via type. The iNets' feature supports multiple via types for any given layer-to-layer transition and the ACE software is able to identify the unique structure and its S-parameter dataset. Alternatively, ACE technology can use a closed-form model to netlist the via based on the geometric description of layers, pads, and drill holes. If the user provides neither S-parameters nor specifies a closed-form model, the ACE software will default to the use of a simple RLC model of the via.

## Speed

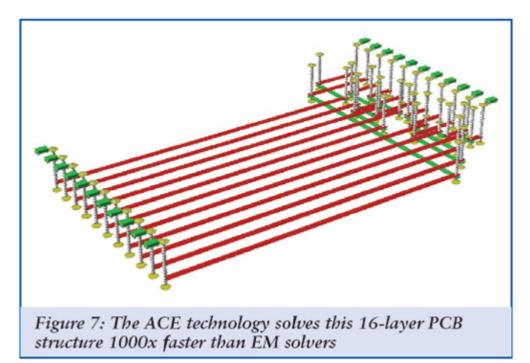

When using the most accurate of EM-based models, the ACE product's speed is the result of reducing the size of the EM problem to one where highly optimized EM solvers can be brought to bear on much smaller structures. In this mode, the software performs at 1000x or more than traditional, generalized EM solvers. The rather simple control line structure on the 16 layers of FR4 shown in **Figure 8** takes approximately four hours for 200 frequency points with a 3D planar MOM solver, but less than 10 seconds using the ACE methodology.

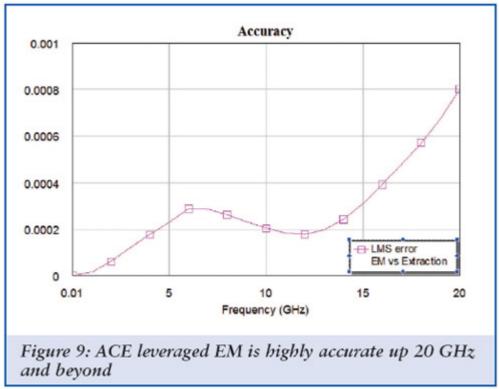

### Accuracy

Fast extraction is useful early in the design flow, becoming less so as the design solidifies and often demands greater accuracy. Since the ACE software uses distributed models (X-models derived with EM) and EM-based models with optimized, built-in EM

solvers, it sustains accuracy much later into the flow and at a higher frequency. For a simple coupled line structure (**Figure 8**), ACE broadband models can provide accuracy within 0.01% of EM analysis (**Figure 9**) in a matter of seconds.

### Summary

Circuit design in recent years has become over-reliant on EM analysis because microwave/RF design tools have not kept pace with the challenges of next-generation design. AWR has a rich tradition of leveraging its considerable experience in microwave design in order to provide innovative EDA solutions that dramatically improve design productivity and reduce product development costs for communications applications. AWR's ACE innovation puts the power of the design process back into the engineer's hands because it provides the user with the ability to parametrically investigate designs by combining the proven technique of circuit extraction with microwave models and understandings. The new software brings to the RF/microwave world the ability to model complex interconnects quickly and accurately, and, most importantly, to perform accurate and timely simulation and analysis early in the design cycle, before timeconsuming design re-spins and costly hardware adjustments are necessary. Users of ACE software can be confident that this new technology will enable them to develop products more quickly and confidently, helping them take advantage of ever-smaller market windows.

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微 波、射频、天线设计研发人才的培养;我们于 2006 年整合合并微波 EDA 网(www.mweda.com),现 已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典 培训课程和 ADS、HFSS 等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子 工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、 研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电 子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

## 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电 路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材; 旨在 引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和 研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格 的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程,共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系 统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又 全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设 计方面的内容。能让您在最短的时间内学会使用 ADS,迅速提升个人技 术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

# HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最 专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月 免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅…

课程网址: http://www.edatop.com/peixun/hfss/11.html

# CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装,所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送 3 个月免费学习答疑…

课程网址: http://www.edatop.com/peixun/cst/24.html

## HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线,让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

## 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了 13.56MHz 线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

### 我们的课程优势:

- ※ 成立于 2004 年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

# 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

专注于微波、射频、天线设计人才的培养 **房迪拓培训** 官方网址: http://www.edatop.com

甸宝网店:http://shop36920890.taobao.cor